�ѵ���Ƭ������������ϸ�����

��������˼�߹�¡�ط������������ҵ�統ǰ��¼��һ��������ϴ�����FPGA

ȫ��ɱ��ƽ̨�쵼��������˼��˾��ǰ�Ƴ�����Virtex®-7 2000T FPGA����������68�ڸ�����ܴ�������������ϴ�Ŀɱ����������Ϊ�ͻ��ṩ�������ױȵ�200�������Ԫ���൱��2,000���ASIC�ţ�ר�����ϵͳ���ɡ�ASIC����Լ�ASICԭ�ͺ�ģ�������г�����

����˼��˾ȫ������ܲü���̫��ִ���ܲ������ˡ�����˼��˾��Ʒ�г�Ӫ���ܼ�Brent Przybus������˼��̫�����ۼ��г��ܼ���������ý����ܲ�չʾ��Virtex-7 2000T��

�����塢�����˺�Brent PrzybusչʾVirtex-7 2000T

��ԽĦ�����ɵ��ش���̱�

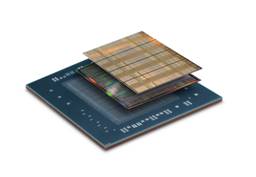

����ʷ�Ͽ���FPGA��Ʒϵ���еĽϴ�����ͨ���ǽϺ����ͻ��Ƴ��ģ�������Ϊ�뵼�幤�յķ�չ��һ����б�µĹ��̣��ϴ������ĵ�λ��Բ���ʴﵽһ��ˮƽ�����ھ������������У�������Ҫʱ��ġ�����˼�� SSI ����ͻ������һ��ս��ͨ�����ĸ���ͬ FPGAоƬ����Դ���н���ϻ���������������ϴ������Ŀɱ�����������Ӷ��������ȱ�ݴ��͵�оƬ��������ս��

����Ϊֹ��FPGAÿ�����սڵ�ķ�չ����ѭĦ�����ɣ�Ҳ�����ڳɱ������ͬʱʵ���������ķ��������ҵ��ǣ���������Ħ�����ɣ��ɿصĹ��ĺʹ����������������г�����Դ��ֹ�������ѵ���Ƭ������SSI������������˼����Ϊ�г��Ƴ���һ���ܹ�Ӧ��������ս�Ŀ��еĿɱ�̽��������

���ڶѵ�����������Virtex-7 2000T

Virtex-7 2000T�ѵ�����

�����˱�ʾ���ѵ���Ƭ����������Ӧ�óɾ�������˼������FPGA����2.5D IC�ѵ�����������Ӧ�ã�ʹ������˼�ܹ�Ϊ�ͻ��ṩ������ͬ�ྺ����Ʒ����������ԽĦ�����ɵķ�չ�ٶȣ������ǵ���ƬFPGA��28nm���սڵ���������ʵ�ֵġ��ͻ���������˼ Virtex-7 2000T FPGA�������������ASIC��������Ͷ��ɱ��൱������£��ѿ���ʱ�����2/3��ͬʱ��������ϵͳ�����ϵͳ����������Ϊ������I/O��������������ġ�������Լ����Ƚ�ASICϵͳ��ԭ����ƺ�ģ����档

��ָ����Virtex-7 2000T FPGA��־������˼���º���ҵЭ��ʷ�ϵ�һ���ش���̱������ڿͻ����ԣ����ش������������û�жѵ���Ƭ��������������Ҫ���ݽ�����һ�����ռ��������п����ڵ���FPGA��ʵ����˴�ľ�������������ڣ�����Virtex-7 2000T FPGA���ͻ�������Ϊ������������µĹ��ܣ����ز���ASIC������FPGA����������ܴﵽ3-5��FPGA��������Ĺ��ܣ�����ɴ�����ͳɱ����������ھͿ��Կ�ʼ�������ǵĽϴ�����FPGA����ԭ����ƺ���ϵͳ����������ͨ���ĸ��»����ٶ���ȣ����ٿ�����ǰһ��ʱ�䡣

�Ƚ����մ���������

����˼����28nm������Artix™-7��Kintex™-7��Virtex®-7 FPGA�� Zynq™-7000 EPP��������ͳһ�ܹ����ܹ���ͬһϵ�еIJ�ͬ��Ʒ���Լ���ͬϵ�еIJ�Ʒ��֧����ƺ�IP���á���Щ����������̨�����28nmHPL�����ĸ߽������բ�������������죬�������������FPGA��̬���ı�ͬ�ྺ����Ʒ����һ�롣������������������̬���Ľ��͵�����Խ��������Virtex-7 2000T ����ڲ��ö��FPGAʵ�ֵ���Ʒ������ԣ����ĸ��ͣ�����28nmHPL���˹ؼ����á�

Virtex-7 2000T������Ϊ�豸�������ṩ��һ�����ɵ�ƽ̨���ܰ����������������ܺ��ܵ�ͬʱ�����ġ����������˵�·���ϲ�ͬIC���I/O�ӿڣ�ϵͳ�����幦�ĵ����������͡�ͬʱ����Ϊ��·������Ҫ��IC�����������٣��ͻ��ܽ��Ͳ����嵥�ɱ������ԺͿ����ɱ������⣬����оƬ�ڹ��н���ϲ��ŷ��ã�SSI�����ܹ�������оƬ�ѵ���ɵĹ��ĺͿɿ������⡣�н����ÿ��оƬ���ṩ10,000������ٻ�������֧�ָ���Ӧ������Ҫ�ĸ����ܼ��ɡ�

�������һ��ϵͳ���ܺ��ܵ�ͬʱ���������豸���������ٵĹ�ͬ��ս��Ҫ��ʵ������Ŀ�꣬һ��;������ͨ��ϵͳ���ɣ����ٰ��ϲ�ͬIC���I/O�ӿ��������Ӷ������ġ�������ΪI/O�ӿ������Լ�I/O�������빦�ij����ȡ��������Խ�ߣ�ϵͳ��IC����Խ�࣬����Ҳ��Խ���Ҫע�⣬�����ʹ�õ� IC �������࣬�ڲ�ͬ�����������Ʒ������Ѷ�Ҳ��Ӵ���Ҳ���ӳ��������ڣ���߲��Գɱ��������� Virtex-7 2000T �������ܱ����������⡣

������Щ֮ǰ��ϵͳ�в��ö��FPGA��ͨ�š�ҽ�ơ����Բ��������պ���������Լ������ܼ��������������Ա��˵��Virtex-7 2000T��ʹ������������л��ߴ���I/O������ͨ��Ƭ���PCB���������ڵ�FPGA���������ɳ�����ܵ�FPGAоƬ�ڸߴ�������ʱ�ӡ����Ļ������Ƶ����ơ�

��ЩӦ�ö���Ҫ������

Virtex-7 V2000T FPGA������������Ƭ���ѿ�ʼ�������ͻ����ھ���������ƣ��������7ϵ��FPGA�������Լ۱Ⱥ͵������ơ����ö��FPGAʵ�ֵĵ�Ч�����ȣ���Virtex-7 2000T��������Դ���ó���70%������£����Ľ���ǰ�ߵļ���֮һ��

ASIC�ľ�������������

Virtex-7 2000T FPGAΪ�ͻ��ṩ��ͨ��ֻ�д�����ASIC�ž߱������������ܺ���ˮƽ���������˿��ر�̵����ơ�����Խ��Խ���ϵͳ���г���ASIC�Ŀ����ɱ��е����Գ��ܣ�Virtex-7 2000T FPGAΪ��Щ����ASIC�����պͳ���5,000����Ԫ��28nm����IC NRE�ɱ�����ƣ��ṩ��һ�����صġ�����չ��������������

Virtex-7 2000T FPGAΪ�ͻ��ṩ��������ͬ�ྺ����Ʒ��������ͬʱʵ���˸���ϵͳ���ɶȣ�֧�ָ���ɫ��ASICԭ�ͺ�������ܡ����⣬����һ�������ϣ�����˼��ͨ������Ƭ���������ܹ�����Ϊ�ͻ��ṩ�ϴ�������

Vitex-7 2000T��������ҪĿ���г���ASICԭ�ͺ�ģ����档��ASICԭ�ͺ�ģ�������ԣ��ͻ�ϣ�������ý�����FPGA���������������ڸ���ϵͳ���������г���Ҫռ�ô�����ʱ�䣬���Ҫ�ǵ�ASIC��ɺ�ſ�ʼ���������������ᵢ������ϵͳ�Ŀ������ȣ���ʱ����Ҫ����2���ʱ�䡣����Virtex-7 2000Tԭ�ͻ�ģ�����ƽ̨��SoC �����������ܴ����ǰ��������ԱҲ�����ٿ��ASIC����ɡ�

��28nm���ռ����ڵ㣬ASIC��ASSP��NRE����5,000����Ԫ����ASIC������ܽ��ɱ���������һ�롣��ˣ�����������ȶ��Ĵ������г�Ӧ�ã�����ASIC��ASSP�����ֻ��Խ��Խ�ٱ����á����⣬���������̲�Ʒ����ʱ�����Щ�г�ѹ��ҲΪ����ASIC�Ŀ�����������ս���ڴ�����£���һ��Virtex-7 2000T���������ASIC������ʵ������Ҫ��ϵͳ���ܺ��ܡ�

����Ķ�:

- ...2011/10/28 11:47���������˼ Virtex-7 2000T FPGA �Ͷѵ���Ƭ��������

- ...2010/10/28 15:13����ԽĦ������ ����˼ȫ�����ѵ���Ƭ��������

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����