DSP����Э�����и��ٴ������ݷ���

�ź�������

�����������ϵ��ź������Բ����Ѿ���Ϊ�����Ա������������Ҫ��ɲ��֣���PCI Express 2.0������ATA III��HDMI 1.3��һ���Բ�������������������Դ�ڲ����ϵIJ������ص㣬�������������Ͷ�ʱ���䡣���б���խ�˶�ʱ���ޣ�Ҫ������������ṩ����Ĵ������ߵľ��ȡ����ͬʱ����Ҫ��ʹ����������Ӱ��ﵽ��С����

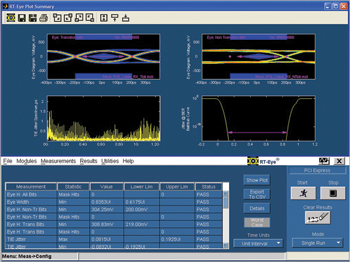

��ͼ����

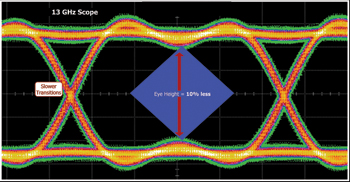

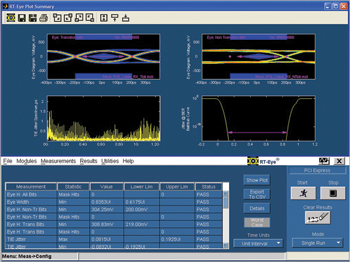

ʾ�����Ĵ���Ӱ����������Ҫ���ź���ͼ����ͼ��һ����ҵ��ʾ����ͼ��Ҳ��һ���Բ��Ժ���֤���ԵĻ�ʯ������ʾ1�����ݡ�λ����λ��������п��ܵı��������״̬��������һ�����Ƶ���ͼ�С��õ�����Ļ�����Ĵ�����������ſ��������Χ��ʾ�����IJ��ι켣�����е����۾��������ſ��̶����������ź�����(���ſ�����Խ��Խ��)���������豸����������ͼ�����ڲ������״̬��1����״̬��0��������ȷ������������Ӧ��ͨ����ʹ��ͼ�Ρ�ģ�塱������ͼ����ͨ��/ʧ�ܵ�����

�ڲɼ��ź�ʱ�����������ʾ���������ķ��ȿ��ܻ�ߴ�1 dB (��ֱ����)���ź����ǣ��������һ���������ͼ�ſ��������У�ǡ���ǽ��ж������ж��ĵط�����ˣ�����Ĵ�������ͼ���������ز�����������Ҫ��

���˵��ǣ������г��ϳ��������������������ṩ�Ϲؼ��Ķ�ʱ�ͱ��ز���Ҫ��Ĵ��������µĴ��з�����ӵ��20 GHz�Ĵ������ټ�������ͨ����50 GS/s�IJ����ʣ��������㵱ǰʹ�õ�ȫϵ�д������ߵ����� ������Щ�����ϣ����α���10-90%���ֵ���������ʱ���Ϊ22 ps�����籾�ĺ������۵�����������DSP�Ĵ�����ǿ�����ṩ��ֱ���Ͽ��ٵĵ�һ�����б������г����Χ��ƽ̹��Ƶ�����ܡ���һ����Ҳ��֤������ͨ���еĽ���Ƶ�ʺͷ�����Ӧƥ�䡣

����������

�������һ���������߽ṹ������������Ҫ������2.5Gbit/s��3.125 Gbit/s֮�䣬��Щ�����ƺ���ȫλ�ڵ�ǰ4GHz��5 GHz ʾ�������ƿط�Χ�ڡ����ǣ��źű���Ȳ�����Ҫ�Ĵ���Ҫ�ߵö࣬������������Ѿ���ʶ��������������ָ���ٶ��㹻����������Բ���ʱ���źŵĵ����г����

��������г��Ϊ�춨�ͷ�����������ʱ���ź��ṩ������ľ��ȣ�ͬʱΪ��֤ȷ�Ľ���ṩ�˸����������

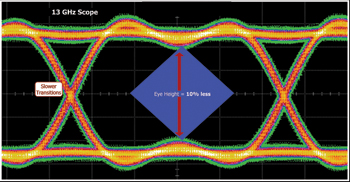

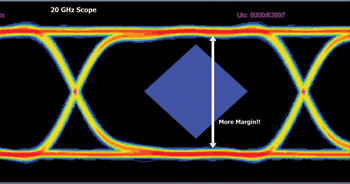

ͼ1˵����������ǿ�����������ر��ǣ���˵����20 GHz ʾ������13 GHz ʾ����֮��IJ��죬�����������ߵ�������6.25 Gbit/s ������PCI-E Gen2�ź����ṩ������Ҫ�ߵöࡣ��20 GHzʱ������������г�����ڷdz����ɾ��ġ���ͼ�п������Կ����������������13 GHz ʾ�����ϣ�û���㹻�Ĵ������������źţ��ź�����ģ�����档

ijЩ��С�飬�ر���PCI SIG����Ŭ��ȷ����������г�������ṩ�ľ��������

��·�ṹ

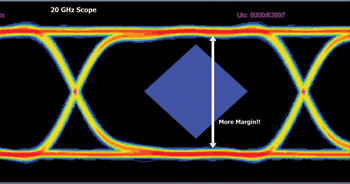

����Ĵ������ߣ������ڶ����͵������������߽ṹ����HDMI 1.3��SATA III��PCI-Express 2.0���ڵ�·Ӧ�����ṩ�˸��ߵ����ܣ�ͬʱ����Ҳ��Ϊ�����������߽ṹʵ�֣�����ö���ͨ·��ʵ�ָ��ߵ����ݽ������ʡ��ڶ�·�����У��������ݰ��ȱ��ֽ⣬Ȼ�������ͬʱͨ��4����8�������ġ�ͨ·�����д���(ͼ2)���ڶ�·����������ִ����֤����Թ����������Ա��Ҫ���Խ��������ͬʱ��4����4�����ϵ�ͨ·�в���ʵʱ���ݣ����ṩ��Ҫ�����ܣ��������һ������������������֤�У������������ź�ͨ·��ͬʱ�������ݣ���ʵ��ʱ����ء��г��������ṩ��ʵʱ�����ʸߴ�50 GS/s����������������������ͨ����ʵ�ֽܳ���ʱ��ֱ��ʣ�ͬʱ��ȫ��4��ͨ���ϲ���4 ms��ʱ����صĴ�������ҵ������ʵʱ������������洢�����ϣ�ʹ�������Ա�ܹ���ÿ��ͨ·�з�����������¼���֮ǰ��֮��������ҵ����صĴ���

��������

�����Ǵ������߿�����Ա��ע����һ�����⡣��ijЩ����£�����������Ը����źű��ص�Ӱ�죬������Ҫ���ǣ���������ͼ�����з�����һ�������á������Խ��������غ��½�����ص���ͼ���ȣ����ܻᵼ��ģ��Υ�档

����۲쵽��������ô���������Ա����豸���������������µIJ�����������ʾ�����Ĵ��������Ͷ������(JNF)���ܻ�Ӱ���õĶ��������ǿ��ܻ�ʹ��ͼ��խ���������Ե�ģ��ʧ�ܡ�

ҵ���Ѿ�������������Ƶ�����У����������ʹʾ�����Ĵ��������ﵽ��С�����ַ����������Ƶ�Чʱ��ɼ�ģʽ�µ����ܣ����б����ÿ���������´����ɼ������ǣ����������Ի��ڵ���ʵʱ�ɼ��Ķ�������û��Ӱ�졣����������£�JNFϵ����Ӱ���Чʱ�䲶���ʵʱ����

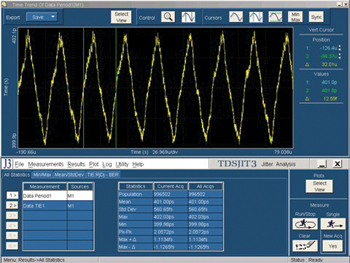

���õķ�����ʹ���ڴ�ֱģ��ת������ӵ�г��㶯̬��Χ(�紹ֱ��)����������ʵ�ָ�����ȼ����͵�JNF (����ֵΪ400 fs RMS)������ʾ��������ʵ�ֶ������������������Զ�����Ӱ�첻��(ͼ3)��

������Ƶ������һ����ս������ʾ��������������ì�ܵ�����ʾ����Ҫ����ϸ�Ķ�ʱϸ�ڣ�ͬʱҪ�ںܳ���ʱ������ʵ����һ�㡣Ϊ���㹻�ķֱ��ʲ���ϸ�ڣ�ͨ���������ϴ������(��50 GS/s���൱��20 ps�IJ������)�����������Ը�����Ѹ���ۻ��ڲ��δ洢���С����ǣ���Ƶ�������ƻ��ڼ��������γɡ���ˣ��������Ҫ�����㹻���������ڣ�ȷ����Ƶ�����Բ�����Ӱ�죬��ô��Ҫ�dz���Ĵ洢����

�Դ洢����ÿ��ͨ���ߴ�200 M�������������ȫ���������¿��Դ洢�ϳ�4 ms�IJ������ݡ�����ʦ���Բ鿴���������ϼ�����������ں�����ͬһ���μ�¼�����仯�е����붶��ϸ�ڡ�

ȥ������Ӱ��

�����������е����˱�Ҫ��Ӳ��������ȥ������ͨ���Ĵ���Ӱ�죬���з�ʽ֮һ��Ӧ�������˲�����ʾ�����ڲ�ִ����ǰҪ������͵���Ӧ�������ļ��������

�ź��˲����տ����ݵ�ģ���������������ʱ������ʱ�˲���������ɢ�ĵ��������������͵������ɵ�һ����·���ڵ�ǰ��DSP�����У��˲�����һ���IJ�����״���༴Ƶ�ʳɷֵ���ѧ�������ںܴ�̶�����ԭ����ģ���˲�����ͬ�����ǣ��������ַ�ʽ�����źţ��Ӽij˷���������ʽ��ִ�и��ֺ������㡣

��һ���̰�����FIR (����������Ӧ)�˲�������������������ϵͳ�С������˲����Ӳ�����ȥ������ó�������ص㣬ʾ������ʾ���������IJ������ߡ�������һ�����ܲ�������Ӱ�����ͼ���Լ��ܹ���ȷ�ط�ӳ�����û�Ӧ�����豸�����ص����ͼ��

ͨ����Ϊ�ź�·�����ɷָ��һ����ʹ��FIR�˲���������ʵ�ֹ㷺�������˲��ص㼰�����ٴ��в������������ܹ��������ܻ�õ��źŵġ�������Ե㡱��

����ǰ��ģ�⼼����ȣ�DSP�˲����������˾��ȡ����ԶȺ��ȶ��ԡ�FIR�˲����ȶ������������ֳ�������λ��Ӧ��������Ƶ�ʻ�����ͬ���ӳ�����ͨ���˲������Ӷ�ʹʧ��ﵽ��С�����⣬FIR�˲�����������Ӧӵ�����Ŀ���������ʱ�����ڣ���˿���Ԥ��Ϳ�����Ӱ�졣

�˲�������������ʾ��������Ӧ�ã�����ʹ���˲�������泣���Ķ�����ٲ������⡣���磬ͨ���˲�������ʦ�������ƴ���������������ͬʱ���ָ߶�ʱ�ֱ��ʡ�������ʹ���˲�������ʾ������Ӧ��Ƶ�ʷ�Χ�߶�֮�ϡ��������ķ�ʽ��

�û�ָ�����ص�

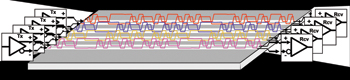

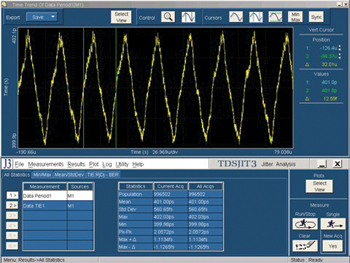

����һ�������ܲ�������ʹ������FIR�˲�����ͨ��������Matlab�����Ƴ����п������û�ָ��ϵ�������Լ��ظı��˲������ص�(ͼ4)��

�����û����Զ�����˲�����Ϊ֧�ָ��ٲ����ṩ��ǿ��Ĺ��ߡ����磬����ź��Ѿ���Ϊ�������������豸���ܵ������Ա��ע��һ���ؼ����⣬�ر����ڲ������յ�Ԫʱ����һЩ�ź���ͨ���κ�̽ͷ����Ե㶼�ò����ġ�

��ʵ֤����������һԭ���ջ�����������������ս�ԡ�����������£������豸�еĽ��ջ�����Բ鿴�ź���˵�Ǽ���û���κ�����Ľ���㣬��Ϊ����Ȥ���ź����豸�ڲ����˲�����������ƫ��ͨ�����¡�PCB�켣������������ʱ�������ӻ���������ջ���Դ���ֵ��źŷ�װ���豸�ڲ������ʹ�ô�ͳ�����Dz��ܻ����Щ�źŵģ����ǣ�������������ͼ�������ص㡣

���������ʹ��DSP�˲�����ģ����ջ��ڲ��˲�����ЧӦ���û���������Ʊ����豸�˲���ʱʹ�õ���ͬ��ϵ�����ص�ʾ�����С���Ӧ���˲���ʾ�����û�����̽��������ţ�ͬʱ�鿴�źţ��������ڲ�̽���豸һ�������֡�������Ե㡱��ʾ�˽��ջ��˲�����źţ���ʹ�������Ե����豸��װ�ϵ�һ����š�������̳�Ϊ����Ƕ����

����ʹ�û���DSP���˲�����ʵ�ֵ�ǰ��ѡ���ź��˲������������ж�����ƽ��(DFE)��ר�е�DFE�˲����ǵ�ǰ����������շ�����ʹ�õļ�����ʾ�����ڲ��������˲������Խ�������FIR�˲�ϵ��������DFEϵ�����ռ��ص�ʾ�����У���DFE�źŽ��к��ڴ�����

������ʹ��DSP�˲���ʹ���ӵ������豸�ļоߺ͵��µ�Ӱ��ﵽ��С��ͨ���춨��ģ�оߣ�����Ϣת������Ӧ���˲�ϵ����ʾ�����û����Կ������������ⲿ��Ԫ���µ����ƺ��ź��ӻ����˲�����

ʹ��DSP��ǿ�ɼ�����

�����źŴ�����������������ʾ�����ɼ�ϵͳ���ṩ����ô���������ǿƵ�ʺ���λ��Ӧ��ͨ��ƥ�䡢̽ͷϵͳ���ܡ��������Ϊ�������ؼ��ص㡣

����ʹ�û���DSP��ͨ��������ǿ���ܣ�ʵ���쳣ƽ̹�ķ�����Ӧ����λ���Զȡ�����������£�ʾ�����ķ�����Ӧ����������ǵ�����Ƶ�ʷ�Χ�ڻᱣ�ֲ��䣬û�з�ֵ���ݽ����ڴ�ͳʾ�����ɼ�ϵͳ�У���������״̬�Dz���ʵ�ֵģ���ͨ��ʹ��DSP������ʹ������״̬ƽ������������������ƽ����Ӧ�����ַ����ĺô��ǿ���ֱ��ָ���������ޣ�ʵ�ֽܳ��IJ������ȡ����磬��12 GHz ʾ�����У����Բ���Ƶ��Ϊ10 GHz���źţ��侫�Ȼ�������100 MHzƵ�ʵ��ź���ͬ����������Χ�ڣ��źű���Ȼᱣ��һ�¡�

DSP�����������ڸ���������Ƶ�ʹ����ص㡣�����Ŀ���ǿ�����Ӧ�½����ٶȣ����ڱ���˲̬��Ӧ�����ʹ�������֮��ʵ�ֽϼ�ƽ�⡣����̫���ᵼ�¸���ĸ�Ƶ�����ɷֽ������Ƶ�Ρ�����̫�����ܻ�ʹ֧��ȷƽ��˲̬��Ӧ����ĸ�Ƶ�ʷ���˥����DSP���Էdz�ȷ�ؿ��ƹ����������أ����������ƺ�˲̬��Ӧ֮��ʵ�ֽ���ƽ�⣬ʵ�ַdz��ߵ��źű���ȡ�

������ʹ��DSP���ṩ�dz�ȷ��ͨ��ƥ�䣬���а�ÿ��ͨ��У��ͬ����������Ӧ�ص㡣�ڶ�·���м�����ִ��α��ֲ�����ͨ����ͨ������ʱ���ڶ���ͨ���л�ü�����ȫ��ͬ�Ľ�Ծ����Ӧ���м�����Ҫ�����塣Ҳ����ʹ����Щ��������֤��̨����֮��ʵ��ȷ��ͨ��ƥ�䡣

��������̽���ź�·����ʹ��DSP����ʾ����������Ӧ���̽ͷ����ߴ����ɲ�ж��˵��ص㡣

���DSP����Ϊ���ƽ���˲���ʹ�ã���ר����̽ͷ·��������ǰ��ȣ������ܵذ�̽ͷ��Ч���ɵ�ʾ����ϵͳ�У���֤̽ͷ��ʾ�������ϣ�ʵ�ֽ�ƽ̹��Ƶ����Ӧ��

�ܽ�

����ÿ�뼸ǧ��λ�Ĵ������߱��ij��֣��ź�������������ϵͳ�����е���Ҫ�����ڲ�����ߡ���һ�������ܲ��������ṩ���㹻�ߵĴ����Ͳ����ʣ�֧�ָɾ���ȷ�ز�����ٴ��в����ص����ͼ�������˴������߿�����Ա���������ڳ����ڲ���������Щ���߿����ڶԲ���Ӱ���С������£������źŶ��������⣬�����µ������˲����ߣ�ʾ�������Դӽ������������·����Ӱ�죬������Ϊ�������߱��и��ӳ�����Ҫ����ЩDSP�˲����Ѿ���Ϊ�������������豸�в���ȱ�ٵ��豸���ر��Dz�����ǰ����ƽ̨������ƽ̨��ʹ�õĴ���Ԫ��ʱ�����籾��������������������ʹ��DSP���ߣ�����̽ͷ�ͼоߵ�Ӱ�죬���������Աʹ�á�������Ե㡱���鿴����в��ܽ���Ľڵ��г��ֵ��źš�

�����������ϵ��ź������Բ����Ѿ���Ϊ�����Ա������������Ҫ��ɲ��֣���PCI Express 2.0������ATA III��HDMI 1.3��һ���Բ�������������������Դ�ڲ����ϵIJ������ص㣬�������������Ͷ�ʱ���䡣���б���խ�˶�ʱ���ޣ�Ҫ������������ṩ����Ĵ������ߵľ��ȡ����ͬʱ����Ҫ��ʹ����������Ӱ��ﵽ��С����

��ͼ����

ʾ�����Ĵ���Ӱ����������Ҫ���ź���ͼ����ͼ��һ����ҵ��ʾ����ͼ��Ҳ��һ���Բ��Ժ���֤���ԵĻ�ʯ������ʾ1�����ݡ�λ����λ��������п��ܵı��������״̬��������һ�����Ƶ���ͼ�С��õ�����Ļ�����Ĵ�����������ſ��������Χ��ʾ�����IJ��ι켣�����е����۾��������ſ��̶����������ź�����(���ſ�����Խ��Խ��)���������豸����������ͼ�����ڲ������״̬��1����״̬��0��������ȷ������������Ӧ��ͨ����ʹ��ͼ�Ρ�ģ�塱������ͼ����ͨ��/ʧ�ܵ�����

�ڲɼ��ź�ʱ�����������ʾ���������ķ��ȿ��ܻ�ߴ�1 dB (��ֱ����)���ź����ǣ��������һ���������ͼ�ſ��������У�ǡ���ǽ��ж������ж��ĵط�����ˣ�����Ĵ�������ͼ���������ز�����������Ҫ��

���˵��ǣ������г��ϳ��������������������ṩ�Ϲؼ��Ķ�ʱ�ͱ��ز���Ҫ��Ĵ��������µĴ��з�����ӵ��20 GHz�Ĵ������ټ�������ͨ����50 GS/s�IJ����ʣ��������㵱ǰʹ�õ�ȫϵ�д������ߵ����� ������Щ�����ϣ����α���10-90%���ֵ���������ʱ���Ϊ22 ps�����籾�ĺ������۵�����������DSP�Ĵ�����ǿ�����ṩ��ֱ���Ͽ��ٵĵ�һ�����б������г����Χ��ƽ̹��Ƶ�����ܡ���һ����Ҳ��֤������ͨ���еĽ���Ƶ�ʺͷ�����Ӧƥ�䡣

����������

�������һ���������߽ṹ������������Ҫ������2.5Gbit/s��3.125 Gbit/s֮�䣬��Щ�����ƺ���ȫλ�ڵ�ǰ4GHz��5 GHz ʾ�������ƿط�Χ�ڡ����ǣ��źű���Ȳ�����Ҫ�Ĵ���Ҫ�ߵö࣬������������Ѿ���ʶ��������������ָ���ٶ��㹻����������Բ���ʱ���źŵĵ����г����

��������г��Ϊ�춨�ͷ�����������ʱ���ź��ṩ������ľ��ȣ�ͬʱΪ��֤ȷ�Ľ���ṩ�˸����������

ͼ1˵����������ǿ�����������ر��ǣ���˵����20 GHz ʾ������13 GHz ʾ����֮��IJ��죬�����������ߵ�������6.25 Gbit/s ������PCI-E Gen2�ź����ṩ������Ҫ�ߵöࡣ��20 GHzʱ������������г�����ڷdz����ɾ��ġ���ͼ�п������Կ����������������13 GHz ʾ�����ϣ�û���㹻�Ĵ������������źţ��ź�����ģ�����档

ijЩ��С�飬�ر���PCI SIG����Ŭ��ȷ����������г�������ṩ�ľ��������

��·�ṹ

����Ĵ������ߣ������ڶ����͵������������߽ṹ����HDMI 1.3��SATA III��PCI-Express 2.0���ڵ�·Ӧ�����ṩ�˸��ߵ����ܣ�ͬʱ����Ҳ��Ϊ�����������߽ṹʵ�֣�����ö���ͨ·��ʵ�ָ��ߵ����ݽ������ʡ��ڶ�·�����У��������ݰ��ȱ��ֽ⣬Ȼ�������ͬʱͨ��4����8�������ġ�ͨ·�����д���(ͼ2)���ڶ�·����������ִ����֤����Թ����������Ա��Ҫ���Խ��������ͬʱ��4����4�����ϵ�ͨ·�в���ʵʱ���ݣ����ṩ��Ҫ�����ܣ��������һ������������������֤�У������������ź�ͨ·��ͬʱ�������ݣ���ʵ��ʱ����ء��г��������ṩ��ʵʱ�����ʸߴ�50 GS/s����������������������ͨ����ʵ�ֽܳ���ʱ��ֱ��ʣ�ͬʱ��ȫ��4��ͨ���ϲ���4 ms��ʱ����صĴ�������ҵ������ʵʱ������������洢�����ϣ�ʹ�������Ա�ܹ���ÿ��ͨ·�з�����������¼���֮ǰ��֮��������ҵ����صĴ���

��������

�����Ǵ������߿�����Ա��ע����һ�����⡣��ijЩ����£�����������Ը����źű��ص�Ӱ�죬������Ҫ���ǣ���������ͼ�����з�����һ�������á������Խ��������غ��½�����ص���ͼ���ȣ����ܻᵼ��ģ��Υ�档

����۲쵽��������ô���������Ա����豸���������������µIJ�����������ʾ�����Ĵ��������Ͷ������(JNF)���ܻ�Ӱ���õĶ��������ǿ��ܻ�ʹ��ͼ��խ���������Ե�ģ��ʧ�ܡ�

ҵ���Ѿ�������������Ƶ�����У����������ʹʾ�����Ĵ��������ﵽ��С�����ַ����������Ƶ�Чʱ��ɼ�ģʽ�µ����ܣ����б����ÿ���������´����ɼ������ǣ����������Ի��ڵ���ʵʱ�ɼ��Ķ�������û��Ӱ�졣����������£�JNFϵ����Ӱ���Чʱ�䲶���ʵʱ����

���õķ�����ʹ���ڴ�ֱģ��ת������ӵ�г��㶯̬��Χ(�紹ֱ��)����������ʵ�ָ�����ȼ����͵�JNF (����ֵΪ400 fs RMS)������ʾ��������ʵ�ֶ������������������Զ�����Ӱ�첻��(ͼ3)��

������Ƶ������һ����ս������ʾ��������������ì�ܵ�����ʾ����Ҫ����ϸ�Ķ�ʱϸ�ڣ�ͬʱҪ�ںܳ���ʱ������ʵ����һ�㡣Ϊ���㹻�ķֱ��ʲ���ϸ�ڣ�ͨ���������ϴ������(��50 GS/s���൱��20 ps�IJ������)�����������Ը�����Ѹ���ۻ��ڲ��δ洢���С����ǣ���Ƶ�������ƻ��ڼ��������γɡ���ˣ��������Ҫ�����㹻���������ڣ�ȷ����Ƶ�����Բ�����Ӱ�죬��ô��Ҫ�dz���Ĵ洢����

�Դ洢����ÿ��ͨ���ߴ�200 M�������������ȫ���������¿��Դ洢�ϳ�4 ms�IJ������ݡ�����ʦ���Բ鿴���������ϼ�����������ں�����ͬһ���μ�¼�����仯�е����붶��ϸ�ڡ�

ȥ������Ӱ��

�����������е����˱�Ҫ��Ӳ��������ȥ������ͨ���Ĵ���Ӱ�죬���з�ʽ֮һ��Ӧ�������˲�����ʾ�����ڲ�ִ����ǰҪ������͵���Ӧ�������ļ��������

�ź��˲����տ����ݵ�ģ���������������ʱ������ʱ�˲���������ɢ�ĵ��������������͵������ɵ�һ����·���ڵ�ǰ��DSP�����У��˲�����һ���IJ�����״���༴Ƶ�ʳɷֵ���ѧ�������ںܴ�̶�����ԭ����ģ���˲�����ͬ�����ǣ��������ַ�ʽ�����źţ��Ӽij˷���������ʽ��ִ�и��ֺ������㡣

��һ���̰�����FIR (����������Ӧ)�˲�������������������ϵͳ�С������˲����Ӳ�����ȥ������ó�������ص㣬ʾ������ʾ���������IJ������ߡ�������һ�����ܲ�������Ӱ�����ͼ���Լ��ܹ���ȷ�ط�ӳ�����û�Ӧ�����豸�����ص����ͼ��

ͨ����Ϊ�ź�·�����ɷָ��һ����ʹ��FIR�˲���������ʵ�ֹ㷺�������˲��ص㼰�����ٴ��в������������ܹ��������ܻ�õ��źŵġ�������Ե㡱��

����ǰ��ģ�⼼����ȣ�DSP�˲����������˾��ȡ����ԶȺ��ȶ��ԡ�FIR�˲����ȶ������������ֳ�������λ��Ӧ��������Ƶ�ʻ�����ͬ���ӳ�����ͨ���˲������Ӷ�ʹʧ��ﵽ��С�����⣬FIR�˲�����������Ӧӵ�����Ŀ���������ʱ�����ڣ���˿���Ԥ��Ϳ�����Ӱ�졣

�˲�������������ʾ��������Ӧ�ã�����ʹ���˲�������泣���Ķ�����ٲ������⡣���磬ͨ���˲�������ʦ�������ƴ���������������ͬʱ���ָ߶�ʱ�ֱ��ʡ�������ʹ���˲�������ʾ������Ӧ��Ƶ�ʷ�Χ�߶�֮�ϡ��������ķ�ʽ��

�û�ָ�����ص�

����һ�������ܲ�������ʹ������FIR�˲�����ͨ��������Matlab�����Ƴ����п������û�ָ��ϵ�������Լ��ظı��˲������ص�(ͼ4)��

�����û����Զ�����˲�����Ϊ֧�ָ��ٲ����ṩ��ǿ��Ĺ��ߡ����磬����ź��Ѿ���Ϊ�������������豸���ܵ������Ա��ע��һ���ؼ����⣬�ر����ڲ������յ�Ԫʱ����һЩ�ź���ͨ���κ�̽ͷ����Ե㶼�ò����ġ�

��ʵ֤����������һԭ���ջ�����������������ս�ԡ�����������£������豸�еĽ��ջ�����Բ鿴�ź���˵�Ǽ���û���κ�����Ľ���㣬��Ϊ����Ȥ���ź����豸�ڲ����˲�����������ƫ��ͨ�����¡�PCB�켣������������ʱ�������ӻ���������ջ���Դ���ֵ��źŷ�װ���豸�ڲ������ʹ�ô�ͳ�����Dz��ܻ����Щ�źŵģ����ǣ�������������ͼ�������ص㡣

���������ʹ��DSP�˲�����ģ����ջ��ڲ��˲�����ЧӦ���û���������Ʊ����豸�˲���ʱʹ�õ���ͬ��ϵ�����ص�ʾ�����С���Ӧ���˲���ʾ�����û�����̽��������ţ�ͬʱ�鿴�źţ��������ڲ�̽���豸һ�������֡�������Ե㡱��ʾ�˽��ջ��˲�����źţ���ʹ�������Ե����豸��װ�ϵ�һ����š�������̳�Ϊ����Ƕ����

����ʹ�û���DSP���˲�����ʵ�ֵ�ǰ��ѡ���ź��˲������������ж�����ƽ��(DFE)��ר�е�DFE�˲����ǵ�ǰ����������շ�����ʹ�õļ�����ʾ�����ڲ��������˲������Խ�������FIR�˲�ϵ��������DFEϵ�����ռ��ص�ʾ�����У���DFE�źŽ��к��ڴ�����

������ʹ��DSP�˲���ʹ���ӵ������豸�ļоߺ͵��µ�Ӱ��ﵽ��С��ͨ���춨��ģ�оߣ�����Ϣת������Ӧ���˲�ϵ����ʾ�����û����Կ������������ⲿ��Ԫ���µ����ƺ��ź��ӻ����˲�����

ʹ��DSP��ǿ�ɼ�����

�����źŴ�����������������ʾ�����ɼ�ϵͳ���ṩ����ô���������ǿƵ�ʺ���λ��Ӧ��ͨ��ƥ�䡢̽ͷϵͳ���ܡ��������Ϊ�������ؼ��ص㡣

����ʹ�û���DSP��ͨ��������ǿ���ܣ�ʵ���쳣ƽ̹�ķ�����Ӧ����λ���Զȡ�����������£�ʾ�����ķ�����Ӧ����������ǵ�����Ƶ�ʷ�Χ�ڻᱣ�ֲ��䣬û�з�ֵ���ݽ����ڴ�ͳʾ�����ɼ�ϵͳ�У���������״̬�Dz���ʵ�ֵģ���ͨ��ʹ��DSP������ʹ������״̬ƽ������������������ƽ����Ӧ�����ַ����ĺô��ǿ���ֱ��ָ���������ޣ�ʵ�ֽܳ��IJ������ȡ����磬��12 GHz ʾ�����У����Բ���Ƶ��Ϊ10 GHz���źţ��侫�Ȼ�������100 MHzƵ�ʵ��ź���ͬ����������Χ�ڣ��źű���Ȼᱣ��һ�¡�

DSP�����������ڸ���������Ƶ�ʹ����ص㡣�����Ŀ���ǿ�����Ӧ�½����ٶȣ����ڱ���˲̬��Ӧ�����ʹ�������֮��ʵ�ֽϼ�ƽ�⡣����̫���ᵼ�¸���ĸ�Ƶ�����ɷֽ������Ƶ�Ρ�����̫�����ܻ�ʹ֧��ȷƽ��˲̬��Ӧ����ĸ�Ƶ�ʷ���˥����DSP���Էdz�ȷ�ؿ��ƹ����������أ����������ƺ�˲̬��Ӧ֮��ʵ�ֽ���ƽ�⣬ʵ�ַdz��ߵ��źű���ȡ�

������ʹ��DSP���ṩ�dz�ȷ��ͨ��ƥ�䣬���а�ÿ��ͨ��У��ͬ����������Ӧ�ص㡣�ڶ�·���м�����ִ��α��ֲ�����ͨ����ͨ������ʱ���ڶ���ͨ���л�ü�����ȫ��ͬ�Ľ�Ծ����Ӧ���м�����Ҫ�����塣Ҳ����ʹ����Щ��������֤��̨����֮��ʵ��ȷ��ͨ��ƥ�䡣

��������̽���ź�·����ʹ��DSP����ʾ����������Ӧ���̽ͷ����ߴ����ɲ�ж��˵��ص㡣

���DSP����Ϊ���ƽ���˲���ʹ�ã���ר����̽ͷ·��������ǰ��ȣ������ܵذ�̽ͷ��Ч���ɵ�ʾ����ϵͳ�У���֤̽ͷ��ʾ�������ϣ�ʵ�ֽ�ƽ̹��Ƶ����Ӧ��

�ܽ�

����ÿ�뼸ǧ��λ�Ĵ������߱��ij��֣��ź�������������ϵͳ�����е���Ҫ�����ڲ�����ߡ���һ�������ܲ��������ṩ���㹻�ߵĴ����Ͳ����ʣ�֧�ָɾ���ȷ�ز�����ٴ��в����ص����ͼ�������˴������߿�����Ա���������ڳ����ڲ���������Щ���߿����ڶԲ���Ӱ���С������£������źŶ��������⣬�����µ������˲����ߣ�ʾ�������Դӽ������������·����Ӱ�죬������Ϊ�������߱��и��ӳ�����Ҫ����ЩDSP�˲����Ѿ���Ϊ�������������豸�в���ȱ�ٵ��豸���ر��Dz�����ǰ����ƽ̨������ƽ̨��ʹ�õĴ���Ԫ��ʱ�����籾��������������������ʹ��DSP���ߣ�����̽ͷ�ͼоߵ�Ӱ�죬���������Աʹ�á�������Ե㡱���鿴����в��ܽ���Ľڵ��г��ֵ��źš�

����Ķ�:

- ...2018/10/18 09:59�����������źſ�������DSC������ʱ��ؼ��Ϳ���Ӧ�õ�DSP����

- ...2017/07/26 17:38��Cadence�Ƴ���Խ����ƶ��ͼ�ͥ����Ӧ�õ�Tensilica HiFi 3z DSP�ܹ�

- ...2017/03/27 20:57���ⷨ�뵼��(ST)��DSP Concepts������ΪSTM32�û��ṩ��ѵĸ���Ƶ��ƹ���

- ...2017/03/10 11:04���ⷨ�뵼�塢DSP Group��Sensory�������������豸�ؼ���������˷�

- ...2017/02/24 08:31��CEVA�Ƴ�ҵ�����ȵ�ͨ��DSP�ں�Ϊ��ǧ�������ṩԽ����

- ...2017/01/12 15:14�������Ƽ����CEVA ͼ����Ӿ� DSP��Ȩ���������ƶ��豸�����ѧϰ

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������

��Ʒ��Ѷ����

��ҵ��������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����