ֻҪ���ˡ�����Ҫ����FPGA���ô����

Achronix����SpeedcoreǶ��ʽFPGA IP��Ʒ���������г�

��ǰ��Achronix Semiconductor��˾�ڱ�������IP��Ʒ��������CEO��Robert Blake�������й����ܾ���Eric Law���������˸ù�˾���Ƴ���IP��Ʒ����������ý��ɷá����DZ�ʾ��SpeedcoreǶ��ʽFPGA�����������������10�������Ľ�����50%���ɱ�������90%����Ҫ���ڷ��������������ļ��١����ߺ�����ͨ�š���ȫ���ܵ���Ҫ�����ܵ�����

�����ܶ���Ӣ��

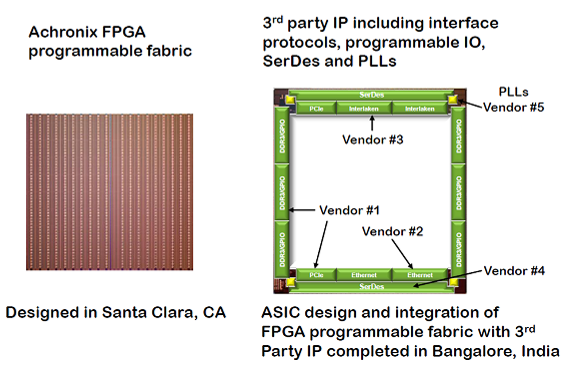

Robert Blake����˵��Achronix Semiconductor��˾�ո��Ƴ��˿ɼ������ͻ�ϵͳ��оƬ��SoC���е�Speedcore™ Ƕ��ʽFPGA��embedded

FPGA ��eFPGA��֪ʶ��Ȩ��IP����Ʒ�������̿�ʼ��ͻ�������Speedcore��רΪ������������Ӧ�ö���ƣ�����Achronix��Speedster22i FPGA������ͬ�ĸ����ܼܹ�������������2013�꿪ʼ�������������пͻ���ʹ�á�Speedcore eFPGA��Ʒʹ��Achronix����ġ�������֤��ACE������ƹ��ߡ�δ����Achronix����������һ��Speedster����FPGA��

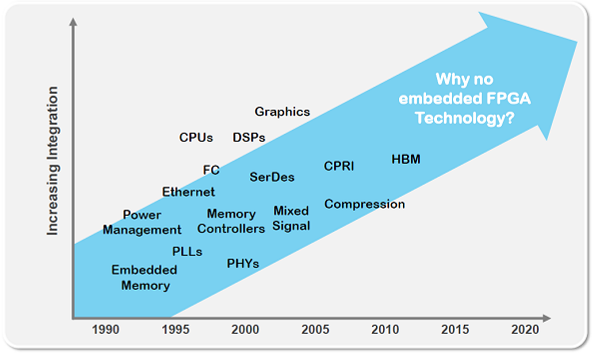

����ʾ���Ͻ����������������ļ�������Խ��Խ�࣬��FPGAӦ���ѽ�������������Ρ���CPUЭ����������һ������TTL���������ڶ����������ӡ��ڵ������Σ�FPGA�����ѹ㷺ʹ�ã�CPU�����������ļ��٣���Ҫ���������������磬������������ʩ���ɱ��Ӳ�����ٿ���������ܣ�FPGAǶ��ʽ����ǡǡ������������������Achronix֮���Կ����ɹ��ṩeFPGA����������Ϊӵ��FPGAרҵ֪ʶ��IP���ɼ�������ǿ����Ƕ��ʽFPGA��һ���ܶȽϸߣ��������������������Ƶĸ�����Ҫ��

���������������Աһֱ��Ѱ��Ƕ��ʽFPGA�����ڶͬ�ĸ�����Ӧ�ã���FPGA��ΪIP���ɵ�SoCоƬ�л��кܶ����ڵ�������Achronix�������������ܼ����Ʒ�Ŀͻ��ṩeFPGA IP��Ʒ��Ϊ��ʵ�ִӴ�����ж����Щ���ܶȼ�������FPGA IP�У��Ӷ�������������������������Ӵ��Ҳ��������ĸ����ܼ���Ӧ���г���eFPGA��Ʒ����Achronix��˾��һ�����˼����Ļ��ᣬҲ�ǰ뵼����ҵ�ľ����á�

�ı���Ϸ����

Robert Blake��Ϊ������Speedcore IP��Ʒ���ͻ����������Ӧ�������ƽϼѵ�оƬ��������ĺ���Դ���á��ͻ����Զ�����ұ���LUT����Ƕ��ʽ�洢���Լ�DSP�����������⣬�ͻ����Զ���Speedcore�Ŀ��߱ȡ����������IO���˿ڵ����ӣ��������ڹ��ĺ�����֮�����Ȩ�⡣Achronix�ṩ��Speedcore IP��Ʒ��GDS II�ļ����ͻ���ֱ�ӽ��伯�����Լ���SoC�У�Achronix���ṩ����ACE��ƹ��ߵ�һ�����ƻ���ȫ���ܰ汾���ͻ���������Speedcore eFPGA�Ĺ��ܽ�����ơ���֤�ͱ�̡�

��˵��������������ͬ�Ĺ�˾��һֱ��̸��eFPGA��Ʒ����Achronix��Speedcore������ͻ�������eFPGA IP��Ʒ��������Ϸ����ĸı��ߡ�Achronix���ǵ�һ���ṩ����Ƕ��ʽϵͳ����IP�ĸ��ܶ�FPGA�Ĺ�Ӧ�̣���������ʹ����ͬ�ġ�������֤�ļ�����ͻ��ṩ��eFPGA��Ʒ����Щ�ͻ���ϣ����ASIC��Ƶĸ��ָ�Ч�ܺ�eFPGA�ɱ��Ӳ��������������Խ����ͬһ��оƬ�С�

eFPGA���Ĵ�����

�ݽ��ܣ��������ĺ���ҵ�еļ�����ͨ�Ż�����ʩ��ָ���������������ʡ����ϱ仯�İ�ȫ���������⻯Ҫ����ǰ�������ٱ���ͬ������ͳ�Ķ��CPU��SoC��Ҫ�ɱ��Ӳ����������Ԥ������ж�����ݣ��Ӷ�������������ܡ�FPGA�ǽϼѵ�Ӳ�������������������Ϊ�����㷨�IJ��ϱ仯����������Ҫ�������µĹ�����ʵ�ָ��¡����ڵ���������Ӧ�ã�������FPGAоƬ��һ�ַ�����ʵ�ʵĽ��������Ȼ�������ڸ�����Ӧ�ã�Speedcore�ǽϼѽ�������������ṩ�Ĵ��������ƣ�

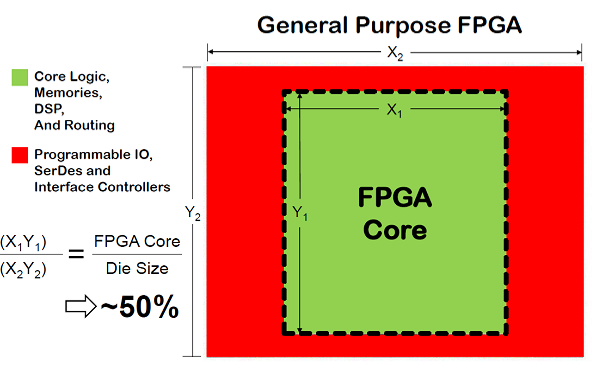

��һ�������Ǹ��͵Ĺ��ģ�Speedcore���ڲ����߷�ʽֱ��������SoC���Ӷ�ʡȥ�������ö���FPGA�пɼ��Ĵ��Ϳɱ������������壨IO buffer�����ɱ�����������·�Ĺ���ռ���˶���FPGA�ܹ��ĵ�һ�롣Speedcore��оƬ������Ը��ݿͻ�����Ӧ�õ���������ƣ�Ϊ�˸��͵Ĺ��ģ��ͻ����Ե������ռ�����ʵ�����ܵ�ƽ�⡣

�ڶ��������Ǹ��ߵĽӿ����ܣ���ȶ�����FPGAоƬ�ӿڣ�Speedcore IP�Ľӿ��ӳٸ��͡����ܸ��ߡ�Speedcoreͨ��һ�������IJ��нӿ�������ASIC����������FPGAͨ��ͨ��һ�����ӳٵĴ�����/�����SerDes���ܹ��������ӡ�

�����������Ǹ��͵�ϵͳ�ɱ�����Ϊʡȥ�˿ɱ������������壨IO buffer���ܹ���Speedcore��оƬ����ȶ�����FPGAС�öࡣ����FPGAӵ�нϸߵ���������Ϊ��֧����Щ���ŵ��ȳ���PCB��Ҫ�϶�IJ���������Speedcore IP���Ա���������⡣���⣬Speedcoreʡȥ�˶Զ���FPGA�ܱ�����֧����Ԫ������������ЩԪ����������Դ��������ʱ�ӷ���������ƽλ��������ԴԪ����FPGA��ȴ������

���ĸ������Ǹ��ߵ�ϵͳ�ɿ��Ժ���Ʒ�ʣ���FPGA�Ĺ��ܼ�����һƬASIC�У���������ӡ�Ƶ�·���Ϸ���һ�Ŷ�����FPGA����ɵĿɿ��Ժ�������ʧ��

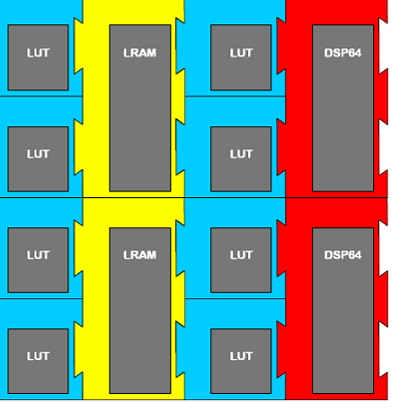

ģ�黯��ʽ����

�ڹ��ռ������棬Speedcore��ģ�黯��ʽ�������Ա�Ϊ�ͻ��ڶ�������Դ����ʱ�ṩ������ϵ�֧�֣�ͬʱҲ֧��Achronix��Դ������������Speedcore IP ��Ʒ��ʵ�ֽ��������⣬ģ�黯�ܹ�Ҳ֧��Achronix����ؽ��������ֲ����ͬ�Ĺ��ռ����ͽ��������ϡ������Ѿ������ṩ����̨���磨TSMC����16����FinFET

Plus��16FF+�����յ�Speedcore IP��Ʒ���������ڿ�������̨�����7�����յ�IP��

��������Speedcore

Achronix��ACE��ƹ��߰���һ��Speedcore��ʵ�����ͻ�����������������������ƣ��������ܡ���Դʹ�úͱ���ʱ��ȷ�������Speedcore IP�����⣬Achronixӵ�й���Speedcore���ܺ�ASIC�������̷���������ĵ���ϣ���˽�SpeedcoreоƬ������ĵ���Ϣ�Ŀͻ�������ϵAchronix���Ի�ȡ���ض�Speedcore�ߴ缰���յ���ϸ���ϡ�

Robert Blake�Ϻ��ʾ����ȶ���FPGA��Speedcore�ṩ�����������ƣ�������������10���������ӳټ�С��1/10�����Ľ���50%���ɱ�����90%��Achronix��Ψһһ�Ҽ��ṩeFPGA�������ṩ����FPGA������FPGA��Ӧ�̡���˾�����ҿ���SoC�Ĵ���˾��������������Ƽ��ɺ���֤������ʹ�ñ���IP��Ʒ��ҵģʽ�����ƹ㣬������Ȩ����Speedcore��������ʹ��Speedcore IP����������������ȡ֪ʶ��Ȩʹ�÷ѣ���ACE��ƹ��߽���ά����

����Ķ�:

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����