3D��ͬ�����������ȱȽ���

����������������ѧ��North Carolina State University������Paul Franzon��ʾ���Ӵ�ͳ��CMOS�ȱ����Ż�����������������Ѿ���ʱ�ˣ�������Ҫ3D���������ҵ��϶��

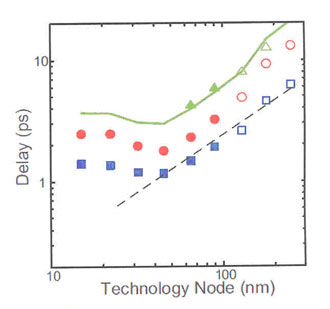

��3D IC�ṩ�������ĵȱ����ţ���Franzon�ڵ��ݰ�˹͡��Austin, Texas�����е�IEEE������װ�����켼����CPMT��������������ʾ����������MITϵͳ����ʵ���ҵ�һ���о����о���������CMOS 32nm������ǰ������ܵĹ������ܽ������ٵõ������������ܹ�����ؽ��ͼ������ݡ�

IBMϵͳ�ͼ������ŵļ������Ծ���Mike Shapiro˵��IBM�������ڿ���һ�ַdz��ɿ���TSV������ͨ�ף����ա�IBM������ʾ��TSV�ij�Ʒ�ʱ�����Ƭ�ϻ����ij�Ʒ���൱������ʹ���þ���Ч�档

Shapiro˵���ƻ���ŦԼ�ݱ���IBM���������ͷ�װ�������ģ�IBM-backed Nanoscale & Packaging Technology Center������3D�����а�����Ҫ��ɫ������2009�����ٵ��Եľ��û�������IBMҵ��ͬ��Ͷ��15����Ԫ��ŦԼ����Ͷ��5

000����Ԫ��Shapiro��ʾ�����з����ĵ�һ���ؼ���Ŀ�ǿ���������һ����Ʒ��3D������ʹ��δ���IJ�Ʒ�ܴ�3D�л�����

Cadence����IC����ר��Vassilios Gerousis˵��Cadence�������ȵ���ҵ���ͻ�����3D�����Ŀ�����Cadence�Ѿ�������һ��3D�������ߺ���Ʒ��������⣬Cadence�����ȵ�3D�ͻ���2008��ɹ���Ƭ��taped out��������45nm���յ�3D�ѵ�оƬ��

����Ķ�:

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����