����BIST�ı�������IP�˲���

�� 1 ����

���Ű뵼�幤�յķ�չ��Ƭ��ϵͳSOC�ѳ�Ϊ����һ����������������IP���õ�SOC�����ͨ���û��Զ�����(UDL)�����߽�IP������Ϊһ��ϵͳ����������Ч�ʣ��ӿ�����ƹ��̣������˲�Ʒ����ʱ�䡣����������ƹ�ģ���������ܶȵ���ߣ�IP���ŵ����࣬IP��ֲ����ȼӴ��Ȼʹ�ò�����֤�������ء���ͳ�ƣ���SOC����У������ں˵IJ�����֤�������õ�ʱ��ռ������ƹ��̵�60����80����SOC��IP�˵IJ�����֤�ѳ�ΪSOC������չ��ƿ��������ڽ϶̵�ʱ���ڸ�ЧѸ�ٵ�ͨ��IP����֤����ԣ������伯����SOC�г�Ϊҵ���ע�Ľ�����о�����ͻ����ʵ�ֵķ���

����IP�˸��õ�SOC����IP�����ͺ���Դ������ͬ����ʹ����֤�õ�IP���ڼ���ʱҲ����ȷ�����������IP�˱����ɵ�SOC������������˿�ҲǶ�뵽SOC��ԭ���ɲ�Ķ˿�ʧȥ��ԭ�еĿɿ��ԺͿɹ۲��ԣ���ò��ɲ⡣

�������һֱѰ����Ч�IJ�����֤���������ĸ����˻����ڽ��Բ��Է���(BIST)������Ʊ�������IP�˵�ͬʱ����������������ƣ��������IP�˿ɲ��ԡ�

2 ���Խṹ

��ν���ԣ������ڱ����·����������ʩ����Ӧ�ļ����źţ�Ȼ����������ŵ���Ӧ����������������ŵ���Ӧ���������ŵ���Ӧ���бȽ����жϵ�·�Ƿ���ڹ��ϵĹ��̡�

IP�˲��Ե�Ŀ�����ڼ��IP���Ƿ���ڹ��ܺ�ʱ����Ӷ���IP�˽����ģ���߲�Ʒ�Ŀɿ��ԡ�һ����÷��ʡ����롢���Ƶ��ֶζ�IP�˵������ʩ�Ӽ������õ���Ӧ����������Ӧ���бȽϡ�Ƕ��ʽIP�˵IJ��Խṹ��ͼ1��ʾ��

���Լ���ԴΪǶ��ʽIP�����ɲ�������ļ�������Ӧ�����������õ�����Ӧ���з����������ͬ�����û�й��ϣ���ͬ��������ڹ��ϡ����Է��ʻ����� SOC�������ݵ�һ���ֶΣ��������Լ������͵�IP�˵�����˿ڲ���������Ӧ��IP�˵�����˿ڴ��͵���Ӧ�����������������IP��ͬ���ʻ��Ƽ�����������֮��Ľӿڣ����������ʵ��Ƭ�Ϻ����֮��IJ��Ը��룬Ҳ����ΪIP���ṩ�˲������ݴ���ͨ����

3 �ڽ��Բ���ԭ��

�ڽ��Բ����ǿɲ�����Ƶ�һ����Ҫ�����������˼�����õ�·�Լ����ɲ�������������ͨ���ⲿʩ�Ӳ����������������������ж����õ��Ľ���Ƿ���ȷ���ڽ��Բ���ԭ��ͼ��ͼ2��ʾ��

���в������(wrapper)��IP�˵����֮�о����Կ��ǡ�ͨ����������ⲿ���Կ���BIST������ģʽ���л�����������ڲ�����ñ߽�ɨ��ģ�顢��λ�Ĵ������·�������ȣ������ʡ����롢���Ƶ����ã������IP�˵Ŀɲ��ԡ�Ȼ�����������ǻ�ʹIP�˵��������������˱�����IP�˵Ŀɲ��Ժ����֮�����Ȩ�⡣

4 �ڽ��Բ��Ե�ʵ��

�ɿ���ָ����һ���ڵ�Ϊ��״̬0��1�����׳̶ȣ��ɹ۲���ָ���ⲿ�˿ڹ۲��ڲ��ڵ���ϵ����׳̶ȣ��ɲ��Ծ���ָ��������·ȫ���ڵ�Ŀɿ��ԺͿɹ۲��ԡ�����Ȼ���߿ɲ��ԱȽ����ײ��������������Ҳ���Ч�����á�

Ϊ�����IP�˵Ŀɲ��ԣ���IP�˵�����оͿ���������ض���·������ԡ���BISTʵ��IP�˵IJ��ԣ�һ������������ƣ����Խӿڣ����Ʋ������������Ͳ��Գɱ�����߲��Կɿ��ԡ�

����BIST�ı�������IP�˲���ʵ�ֿ�ͼ��ͼ3��ʾ��

����ͨ��������ǿ�������/����Ĵ�����������������ʹ���ǻ���Ӱ�죬����״̬�Ͳ���״̬�ܹ��л��������IP�˵Ŀɲ��ԡ������ʵ�ֹ������£�

- ����״̬��ԭʼ�������������������������ٽ�����������ת��Ϊԭʼ�룻

- ����״̬�²�����ǵIJ�����������������������������ֱ�ӽ��������������������������Ϊ������Ӧ�����ʹ��������ֵ�Ƚϣ�ͼ3�е�ģʽѡ��ģ������ṹ��ͼ4��ʾ��

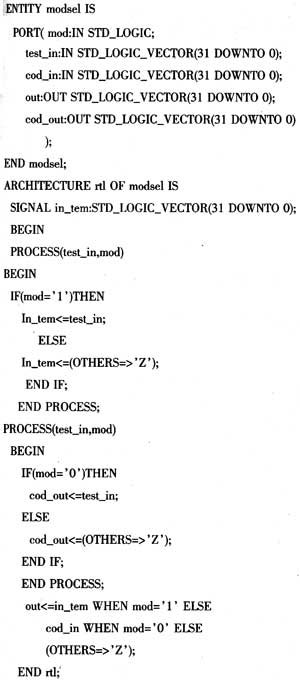

ͼ4��modΪģʽѡ����ƶˣ���0Ϊ����״̬����roodΪ1ʱ��out_sel�����������������in_tem���������in_sel����mod Ϊ0ʱ��cod_out���Ƭ�⣬�Ӷ�ʵ��������״̬�Ͳ���״̬���л���������Ӳ���������Ա�д������·����VHDL�������£�

��ģʽѡ��ģ��ʵ��״̬֮����л�����·������ʵ�֡�

5 ������

BISTΪǶ��ʽ�ں˵IJ����ṩ��һ���ɽ���ķ����������Ч�����ԣ����ϸ����ʽϸߣ�ʵ�ּ�ͨ�����������ǿ���ʵ�ֶ�IP�˵ķ��ʡ����롢���ƣ���Ч�������IP�˵Ŀɲ��ԡ����Dz���BIST��ʹ��·������Ӷ������������IP�˵Ŀɲ��Ժ����֮�����Ȩ�⡣

����Ķ�:

- ...2012/07/04 17:16�����ڣ£ƪ��УӣϵĴ�����վ���ͻ�����������

- ...2012/04/13 11:46�����ڣ£������˲����Ľ���ģ�����Ϳ��Ƶ����

- ...2012/03/14 16:02������BP������ij�����ˮ��վԤ��ģ��

- ...2012/03/13 16:03�����ڣ£�������ģ֣֣�ˮ����ϵ��Ԥ��

- ...2012/02/22 16:27�����ڣ£�����ķ��ֵ�ص���ת�������о�

- ...2010/03/03 08:34������Blackfin�������ļ̵籣�����������������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������