TI C64x+ DSP CACHE һ���Է�����ά��

���ߣ��������� DSP ����Ӧ�ù���ʦ ����

ժҪ

�ڸ��������źŴ���ϵͳ�У�CACHE���㷺�����ֲ�Core��洢��֮����ٶȲ��졣��CACHE��ʹ�ù����У����ڲ�ͬ���ʹ洢��֮�������Ƿ�һ�µ����⡣�������ط���TI������C64x+ DSPϵ���и���CACHE֮������һ���������Լ���ν���һ����ά����

1.����

CACHE��ΪCore�͵��ٴ洢��֮������������ڴ�������ݵ�ʱ��Ϳռ�����ԣ��Կ�Ϊ��λ��Ӳ���������Զ�����Core����Ҫ�Ĵ�������ݡ�������г�������ݵĴ�ȡ����Core��ɣ�����CACHE�����л��ƣ�Coreʼ���ܹ��õ��洢���н��µ����ݡ����ǵ����������Ը��Ĵ洢�����ݵIJ�������ʱ�����粻��ҪCore��Ԥ��ֱ�����ݴ�ȡ��DMA�����棬�Ϳ��ܳ�������CACHE�Ĵ��ڶ�����Core����DMA���ܹ��õ��������ݵ�����Ҳ����CACHEһ���Ե����⡣

2.C64x+ �洢����֯�ṹ

TI�Ը�����C64x�˽����˸Ľ���ʹ�����ܴ����������֮ΪC64x+DSP�ˡ�����C64x+�˿�����DSPоƬ�����в������Խ������磨SCR��Ϊ��������������SCR�ϵIJ�����Ϊ���ࣺMaster��Slave��Master����Core��EDMA�Լ����и���IO��sRIO����EMAC�����衣Master����ֱ��ͨ��SCR����Slave�����ݴ��䡣Slave����ÿһ��Core���ڴ棬DDR2����Լ���������ֱ�ӷ������ݴ�������裬Slave֮������ݴ��䣬��Ҫͨ��DMAЭ����ɡ��������C64x+DSP�������ֲ�����ϸ������SCR�����ú�Master��Slave�������

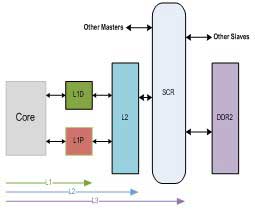

C64x+ϵͳ�Ĵ洢����ͼ��ͼ 1��ʾ���洢�����ֳ�����������һ����L1���������ݴ洢����L1D���ʹ���洢��(L1P)���ڶ����Ǵ�������ݹ��ô洢����L2�������������ⲿ�洢������Ҫ��DDR2�洢����L1P��L1D��L2��CACHE���ֱܷ�����Ӧ��L1P��������L1D��������L2��������ɡ��� 1�ܽ���C64x+ƽ̨�Ͽ��õ�CACHE�����

ͼ 1 C64x+�洢����ͼ

�� 1 C64x+ CACHE����

���ʹ�СLine ��СL1P���룻ֱ��ӳ�䣻�ϴ�32K �ֽ�32 �ֽ�L1D���ݣ�2·�� ������ϴ�32K �ֽ�64 �ֽ�L2���롢���ݣ�4·����д����ϴ�256K �ֽ�128 �ֽ�C64x+ƽ̨��L1P�����洢��������룻L1D�����洢���������ݡ�L1P��L1D��С����32K�ֽڣ����Էֱ�����0K��4KB��8KB��16KB����32KB��ΪCACHE��������Ϊ�����������RAM����ΪCACHE�IJ��֣���������L2��DDR2�����ݻ���롣��ΪRAM�IJ��֣����Դ洢�ؼ��Ĵ����������ʹ��Core�ܹ��Ժܸߵ��ٶ�

C64x+ƽ̨��L2 �洢�������ڴ洢��������ݡ�L2�Ͻϴ���Է���256K�ֽ�CACHE������DDR2�е����ݻ���롣L2�����ಿ����ΪRAM�洢��������ݡ�

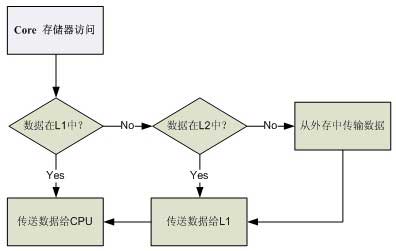

ͼ 2������Core���ʴ洢�����ݵIJ������̡���������������У�Core���ڴ洢���ķ��������ȴ���Core�Ͻ���һ���洢����ʼ��������У�Core����ֱ�ӵõ�����/���ݣ��������/���ݻᱻ���ص�ǰ������CACHE�У��Ӷ�Core���Եõ�Ҫ�����Ĵ���/���ݡ��������̬���ʹ����У�����CACHE�е����ݺ���һ���洢���е����ݿ��ܴ��ڲ�һ�£�����˲̬�IJ�һ�²���������⡣���ǣ����Core��������Master���ܵõ�����һ���Դ洢�����ݸ��º�����ݣ��ͻ����CACHEһ�������⡣

ͼ 2 Core���ʴ洢������

3.CACHEһ�����������

���κ�ʱ�̣�Core��������Master���ʴ洢��������ʱ������CACHE�Ĵ�����ɲ��ܹ��õ��Ͻ����¹������ݣ��ͻ����CACHEһ�������⡣

��һ���ض���ʱ�䷶Χ�ڣ�����CACHE��������һ���洢���е����ݲ�һ���������ġ���ΪCACHE����������һ��ʱ���ڽ����ٴ洢���е������Զ����˵����ٵ�CACHE���ظ�ʹ�á���CACHE�еĿռ䱻����������ռ�õ�ʱ�Ž�CACHE�е����ݽ���ʧЧ����д�IJ�������ʧЧ����д֮ǰ��CACHE�е����ݿ����������洢���е������Dz�һ�µġ�������ʱ�ԵIJ�һ���������ģ�����CACHEһ��������������������������������

CACHE��������Ϊ�����Core��ȡ���ݵ�Ч�ʣ����Գ���CACHEһ��������һ����Core�Դ洢���ķ����йء�Core�Դ洢���ķ��ʷ�Ϊ���ࣺ1.Core������������ݣ�

2.Coreд����������ݡ�

�ݴˣ�CACHE��һ���������Ϊ�������ࣺCore��һ���������Coreдһ�������⡣����������С���У��ֱ������������������ģ�ͣ�

3.1 Core��һ����ģ��

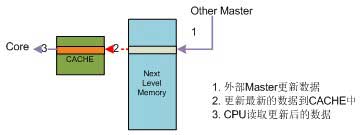

ͼ 3������Core��һ���Ե�ģ�͡������ģ���У�CACHEһ��������Ĵ���ȡ����ͼ������ͷָʾ�ĵڶ��������ܷ���Core��CACHE�����¶�����֮ǰ��ɡ�������ܣ�������Core��ȡ�����ݲ�������Master���º�����ݣ�����ԭ��CACHE�е����ݣ��Ӷ�����һ���Ե����⡣

ͼ 3 Core��һ����ģ��

L1P CACHE��L2�ڴ����DDR2����еĴ�����л��档��Core��һ�ζ�L2����DDR2�еĴ�����ж�������ʱ�����ڴ��벻��L1P CACHE�У�CAHCEӲ���ὫL2����DDR2�еĴ������L1P CACHE�С�Core���Եõ����µĴ��룬������һ���Ե����⡣�˺��������Master����L2����DDR2�еĴ��룬Ȼ��Core�ٴζ�ȡ�˲��ִ���ʱ���ᷢ����Ӧ�Ĵ����Ѿ�����L1P CACHE�У���ʱCore��ֱ�Ӵ�L1P CACHE�ж�ȡ���롣����Core���ܵõ����µĴ��룬�ͳ�����Core��һ���Ե����⡣

L1D Core��һ���������ԭ����L1P��ͬ��ֻ��L1D�������L2����DDR2�е����ݡ�

L2 CACHE��DDR2�еĴ���/���ݽ��л��棬��Core��һ�ζ�DDR2�еĴ���/���ݽ��ж���������ʱ����/���ݲ���L2 CACHE�У���Ҫ����L2 CACHE�ļ��أ�Core���Եõ����µĴ���/���ݡ�֮������Master��DDR2�еĴ���/���ݽ��и��ģ�Core�ض��˲��ִ���/���ݵ�ʱ��Core��������L2 CACHE�е����ݶ�����DDR2�н��µĴ���/���ݣ����Ҳ����Core��һ���Ե����⡣

3.2 Coreдһ����ģ��

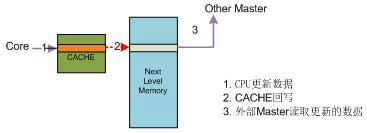

ͼ 4������Coreдһ���Ե�ģ�͡������ģ���У�CACHEһ��������Ĵ���ȡ����ͼ������ͷָʾ�ĵڶ��������ܷ�������Master�Ӵ洢���ж�����֮ǰ��ɡ�������ܣ����������Master�Ӵ洢���ж�����������ԭ�������ݶ�����Core���¹������ݣ��Ӷ�����һ���Ե����⡣

ͼ 4 Coreдһ����ģ��

��Core��L2����DDR2�еĴ���/���ݽ���д������ʱ���������/�����Ѿ���L1 CACHE�У��µĴ���/���ݻᱻ���µ�L1 CACHE�С�������Master��L2����DDR2�ж�����/���ݵ�ʱ��ֱ�Ӵ�L2����DDR2�ж�ȡ��Ӧ�����ݣ����L1 CACHE���µĴ���/����δ�����µ�L2����DDR2�У�������Master��ȡ�IJ��Ǹ��º�����ݣ��ͻ����Coreдһ���Ե����⡣

ͬ����Core���¹��Ĵ���/�����п���ֻ�ǻ�����L2 CACHE�У�����Master��DDR2�ж�ȡ�����ݲ��Ǹ��º�����ݣ�ͬ�������Coreдһ���Ե����⡣

3.3 C64x+һ���Է���

��C64x+�ϵ�CACHEһ�������⣬��Ҫ���ݷ��ô���/���ݵ���Ӧλ�ý��з�����������C64x+ƽ̨�ϣ�L1P��L1D��L2�ڴ�ȿ�����ΪCACHE�ֿ�����Ϊ�洢��ʹ�ã���ˣ��ڷ���һ���������ʱ����Ҫ�������¼������

Case1.������L1P�洢���У�

Case2.������L2�洢���У�

Case3.������DDR2�洢���У�

Case4.������L1D�洢���У�

Case5.������L2�洢���У�

Case6.������DDR2�洢���С�

����Case1�����ڴ���ֱ����L1P�洢���У�����Ҫ����CACHE�����Բ������һ���Ե����⡣

����Case2��Case3���漰��L1P CACHE�����ڴ���ĸ����ܷ�Core���������⡣����ĸ��·ֳ����������һ��Core�����й����жԴ�������ģ���������Master�Դ�����ġ�����������£��������CACHE��һ�������⣬��Ҫ��������ά����

����Case4������ֱ����L1D�洢���У� Coreʼ���ܹ���������Master���µ�L1D�ڴ��е����ݣ�Coreд��������Ҳ�ܹ�������Masterֱ�Ӵ�L1D�ڴ��ж��������Բ������һ���Ե����⡣

����Case5��������L2�洢������������ķ����������CACHE����дһ���Ե����⡣��C64x+ƽ̨����������µ�һ�����������Ӳ���Զ�ά����

����Case6��Ҳ�����CACHE����дһ���Ե����⣬���������Ҫ��������CACHEһ���Ե�ά����

4.C64x+ CACHEһ����ά������

����CACHEһ��������ʱ��Ϊ�˱�֤Core��������Master�ڽ������ݲ�����ʱ���ܹ��õ����µ����ݣ���Ҫ����CACHE��һ����ά��������CACHEһ��������ά��������У������ִ�����ʽ��Ӳ���Զ�ά����Ӧ�ó������ά����

�������������ϼ��������C64x+ƽ̨����ν���CACHEһ�����������

4.1 Ӳ��ά����CACHEһ����

��C64x+ƽ̨�ϣ�Ӳ�����Case5������Զ���������һ����ά����������Ҫ��Ϊ��д����������У�ͼ 5��ͼ 6�ֱ�������Core��L2�ϵ����ݽ��ж���д�������

ͼ 5 Core��L2���ݵ����

ͼ 6 CoreдL2���ݵ����

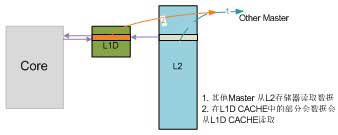

����MasterҪ��L2�е����ݽ��и��²���ʱ��L2����������ݱ��������ݵĵ�ַ�ж���Ӧ�ĵ�ַ�Ƿ���L1D CACHE�У������L1D CACHE�У�Ӳ�����Զ������µ����ݿ���һ�ݵ�L1D CACHE�С���Core����

����Ķ�:

- ...2015/01/20 10:57��TI ����Concerto ˫��MCU ��PRIME ������ͨ�����ݼ���������

- ...2014/12/10 15:08��TI NFC ��Ʒ�����ܵ����е�Ӧ��

- ...2011/11/07 09:50����ζ�dz�ŵ�Ӧ����������� (LiFePO4) ���ʹ�õ� TI �迹���� TM ��ص����ƽ�����

- ...2011/05/20 10:40�������������� TI �� Codec Engine

- ...2011/05/20 10:32��TI ���� Piccolo™ MCU ֧�ֽ��ܿɿ��� LED ��������ҵ�豸�ͼҵ�Ӧ�� - TInergy ϵ�����£�ʮ����

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������