�߹�����ʶ��FPGA��Ƽ���

���ű�Я���Ե�ع����Ӧ�ÿ������ӣ���������ѳ�Ϊ�ӳ�������������ɻ�ȱ�������⣬�ھ�����Ʒ�ߴ硢��������Ч��ʱ������Ҳ��������Ҫ��ɫ�����������Ե��ӵ���������Խ��Խ�̣��߿ɳ������ԣ���������Ϊ��Ʒ���Ӳ��컯���Ե�FPGA������Ӧ���������ܵ����ӡ���ˣ���Ҫ�ﵽ�ϼѵľ�̬�붯̬���ģ�����ȡ����ѡ���ʵ���FPGA�ܹ���

��������� FPGA�ĵ�Դ����

��ͳ��������ѡ��FPGA���ʱ���ɱ���������Ч�ܡ���װ��ʽ�ȣ�ͨ����ϵͳ�ܹ�ʦ�������Ա����Ҫ���ǡ������Ű�����Я���ѵ��ӡ�ҽ�Ƶ�Ҫ����ĵ�Ӧ�ÿ����������ڣ�����Ч��Ҳ�ѳ�Ϊѡ��FPGAʱ����Ҫ���ǡ�һ����˵�������Ա��ASIC��FPGA�ľ�̬�붯̬��Դ���Զ��൱��Ϥ����ȴ���ܲ��˽�����������ʧ��FPGA�߱��б��ڴ�ͳ����SRAM�ĵ�Դ���ԡ�

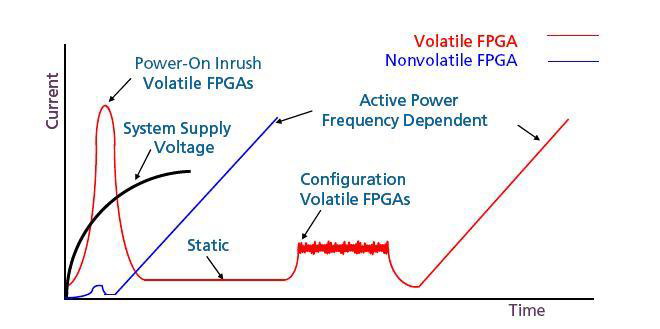

��ʧ��FPGA����������ĵ�ԴҪ�أ���ϵͳͨ��ʱ����������ĵ����õ�Դ(configuration power)���Լ���FPGA���ͨ��ʱ��ɢʧ��ͻ����Դ (inrush power)����ͼ1��ʾ��

����FPGA�İ弶�����Ա��ѡ���Դ��Ӧ�͵��ʱ�����뽫���õ�Դ��ͻ����Դ�����뿼�ǡ����ܻ���SRAM ��FPGA�����̶���ͼ����ͻ���ͱ�̵�Դ�������ڵ�һ��·���������� FPGA�����������ڲ�ͬ�ĵ�·���ϣ�ȴ����ͬ��Դ���������£���������Դ�ɷݻ��ǻ�������صĸ���Ӱ�졣

��ϵͳ��Ƶ����On/Off���ڣ���һ����ĵ�Դ���ľͻ�������أ�����Ԥ���������ʱ��һ��Ҫ�ر��ǽ�ȥ��

���⣬��ʧ��FPGA��Ҫ�ⲿ����PROM��Ϊ���ô��棬��Ҳ����������ĵ�Դ���ġ���ʹ��Щ��������װ�����ڽ��˴����������棬���˶���Ĵ����Դ���ǻ���ڡ�

ͼ1����ʧ��vs. ����ʧ��FPGA�ĵ�Դ����

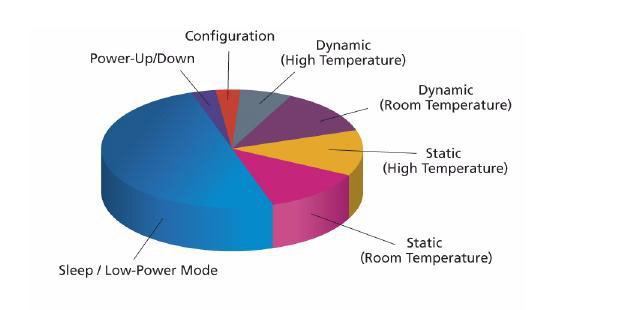

��ˣ�Ҫѡ��һ�ܹ����Ƶ�Դ�IJ���ʱ��ϵͳ�ܹ�ʦ������Ŷӱ����˽�ȷʵ��ϵͳ����ģʽ�Լ����Ӧ�ĵ�Դ�龳����ͼ2��ʾ����һϵͳ�ĵ�Դ������ʾ������ϵͳ���ڲ�ͬ���¶��²��������乤������������ʱ��ȴ�Լ��1:1��

��������ͼ����ʾ��������������ȷ�ĵ�Դ��Ʋ��ԡ���ͼ2�İ�����˵����Ȼ�������Ա���뾡�������¶ȡ���̬���Լ���̬��Դ��

ͼ2��ϵͳ����ģʽ�͵�Դ�ֲ�

ͼ2��ϵͳ����ģʽ�͵�Դ�ֲ�

���;�̬��Դ

ֻҪ��FPGAͨ��֮�����Ƿ���������һ�����о�̬�����������������Ϊ�����©����������������Ź�����С�������أ����ҵ����������ʱ��������¶ȵ���������������Ȼ��̬�������ӣ�������ڶ�̬���������DZȽ�С��

���;�̬���ĵķ�ʽ�кܶ��֣���FPGA�����Ա��˵��Ӧ����ѭ������������ԭ��С�ľ��������ٵ���Դ����ϤFPGA�ܹ���

FPGA��Ʒͨ���������һϵ�в�ͬ�����벻ͬ���ԵIJ�ͬ��������Ϊ������ԽС���侲̬��Դ��ԽС�����FGPA�����ԱӦ����ȷ��Ч��Ŀ������������£�ѡ��ϵ�в�Ʒ�о�����С�������

“���ٵ���Դ”��ָ�������ԱӦ��������RAM��PLL��I/O����Դ��ʹ�á�������˵��Ҫ����I/O�����������Ա�ͱ���ʹ��ʱ�������(time multiplexing)���Լ����ٵ�I/O��������������˼�����Э���ر�I/O��(bank)����һ�����������I/O��������

“��ϤFPGA�ܹ�”��ζ�ţ������Ա���˽�PLL��RC��������I/O ��ȶ�̬��Դ�ĸ��ֲ�ͬ�ϵ�ģʽ����Actel IGLOO FPGAΪ���������ṩ�߲�ͬ��ѹ����ͬI/O������ˣ����ýϵ͵IJο���ѹ�����ܻ����Ÿ��ƾ�̬���ġ�

����·�������Ա�ھ������ܹ�������ѹˮƽ���迹����ʱ��������һ���ؼ��Ľ�ɫ���¶�������Ӱ�쾲̬��Դ������̬��Դ�ķ��������Ӳ�ֻ�ᵼ�¾�̬��Դ�����ӣ�ͬʱҲ����������ص�ɢ�����⡣������ȴ���ɾ���������Χ�¶Ȳ���һ���Ĺ������ر����ڵ�·��ռ�ͳɱ������������¡�

���⣬���������������������ƽ�������迹���ء��Լ������õĽӽŽӵصȣ����ǽ��;�̬��Դ����Ч������

���Ͷ�̬��Դ

��̬��Դ�����¸��ֲ����йأ�

l ʹ�õ�FPGA��Դ��������ģ�顢Ƶ������Ƕ��ʽRAM��PLL��

l I/O�ϵĸ��غ��迹�ն� (resistive termination)

l �������͡��źŻ���л��� (toggle rate)

l �źž�̬������ (probability)

�뽵�;�̬��Դ��ϣ������Ա�ڴ�����̬��Դʱ�����Ϊ�������������� (post-layout)����Դģ��ȷ������ߣ��ȵõ���ȷ����ƶ�̬��Դ�ֲ�ͼ��(power profile)��

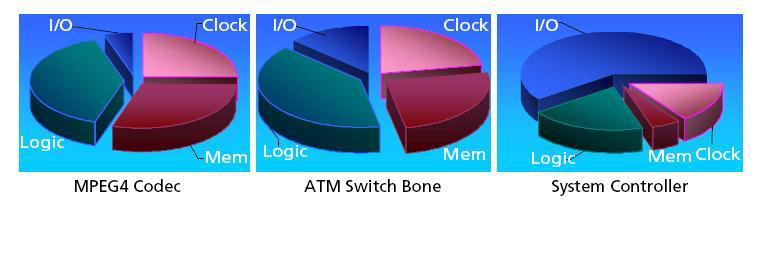

��̬��Դ�ֲ�ͼ���ܹ�������ֳ�ÿ��FPGA��ʹ�õ���Դ����ΪFPGA���е��ԣ�һ����ͬ��װ���ϣ������ж��ֲ�ͬ��Ӧ�����ͣ�������û�������˽�ʵ�ʵĶ�̬��Դ�ֲ���������Ч�ش���������⡣ͼ3��ʾΪ���ֲ�ͬ��������͡�����MPEG�ĵ�Դ�ֲ��������������Ա���⻨ʱ�併��I/O��̬��Դ�����ǣ�����ϵͳ��������˵����Ӧ�ر�Դ�Ż����ȹ����۽���I/O�����ϡ�

ͼ3����ͬӦ���в�ͬ�Ķ�̬��Դ�ֲ�

ͼ3����ͬӦ���в�ͬ�Ķ�̬��Դ�ֲ�

��̬��Դ��Ҫ����RAM��I/O��Ƶ����������Դ����������ɣ����������ֱ���ܽ��Ͳ�ͬ���Ͷ�̬��Դ�ļ��ɡ�

RAM��Դ����

RAMģ���ڶ�/д����ʱ�����ĵ�Դ����Ҫ���Ӱ����źŰ�����ַ�� (address line)��Read Enable (RE)���Լ�Write Enable (WE)��

ͨ������ȡ�ĵ�Դ���Ļ��д���һ�㣬��RAM��/д�ĵ�Դ����������ַ�ĺ������� (Hamming distance) ���Ӷ������ˣ�Ӧ�þ��������ö�ȡ�ź�ǰ���Ⱦ�����ִ�н϶��д�������Ȼ�����л���д�����ǰ�������ܶ�ȡ�ڴ���ȡ����������ݣ�����������Ч���� RAM��Դ���ġ�

�ڽ��ͷ�ֵ RAM��Դ���棬���Կ��Dz��ý���ȡ��д���������Ƶ�ʱ���(clock edge) �ķ��࣬���Ƕ�RAM��/д���ϵ�Ƶ�������ſ� (gate)��

I/O��Դ����

FPGA I/O��ѹͨ���Ⱥ��ĵ�ѹ����ͨ��I/O �� (bank) �����IJ��ٵĵ�Դ����������Ա�ھ���ѡ��I/O�����ӿ�Ƶ�����ӽ����Ƶ����ʱ������Ҫ�dz�������

�ʽ (differential) I/O����LVDS��LVPECL���迹�ն�ʽI/O����HSTL��SSTL�ȣ�ͨ���侲̬��Դ�ϸߣ�����̬��Դ�ϵ͡���ˣ����нϸ��л� (toggle) Ƶ�ʵ������˵������ѡ����ЩI/O��

���� I/O ��������Ҫ�ؼ��������ԱӦ���¿�����������/�������� (partitioning) �Ƿ�ǡ�����Լ��Ƿ������ʱ������� (time-multiplexed) �ķ�ʽ����I/O���������⣬���ڸ��л�Ƶ�ʻᵼ�¶�̬��Դ���ߣ�Ϊ�˽��� I/O�Ļ���л��ʣ������Ա�������� I/O����������˵ķ�Ԥ��ͻ���ź� (glitch)����һ�����ü����ǣ�ѡ��ɽ����л�λ�����߱��� (bus encoding)�����������ϵ�������ֵ������һ��

Ƶ������Դ����

Ƶ���� (clock tree power) ϵ��Ƶ�ʳ����ȣ����Ҳ��������еĻ�Ƿ���У�Ƶ������Դ�Ի�������ġ�����ͳ��Ƶ���ſ� (clock gating) ��������Ч���͵�Դ���ĵķ�ʽ��

��оƬ����Ƶ���ſ�Ϊ����һ�㳣�õ�ϵͳ��Ƶ���ſؼ��ɿ�ʹ����FPGA��Ƶ����ͣ����Чͣ�����еĹ����ԣ�����ֹ�����л������ص����� FPGA���ṩFlash*Freezeģʽ����ϵͳ��Ƶ���ſظ��ߵ��ԣ����Կ�������/���״̬����ֹƵ�ʡ�

RTL����Ƶ���ſ�Ҳ���ձ�ʹ�õ�ʡ�缼�ɣ����л��� latch�Լ�û��latch���������͡���������ʱ����ע��Ƶ��ƫ�� (skew)���Լ������źſ�����ɵĶ����쳣�ź� (glitch)������ͨ���Ὠ��ʹ�û���latch Ƶ���ſ�������AND������˿��ܲ����Ķ����쳣�źš�

���⣬�ֻ�������� FPGA����ж���һ�����ϵ�PLL������Ϊ��Ƶ����Ƶ������Ȳ�������ЩPLLҲ�������Ķ���ĵ�Դ���Թ������е�Ӧ����˵��Ӧ�����ܱ���ʹ��PLL��������˵������Ҫ��Ƶ��������һ��������ȡ��PLL���������µ�Ƶ��Ƶ�ʡ���һ��Ҫ��PLL������뾡��������PLL����������Ż����Խ���PLL����Ľϴ�Ƶ�ʡ�ͬʱ����������� FPGA�е�PLL��һPower-Down ����ӽţ�������Ҫ��ʱ�������ô��������ر� PLL��Ƶ�����硣

����

������FPGA���о��Ͽ�����Ҫ���Ӧ��ʱ��ϵͳ�ܹ�ʦ������Ŷ�Ӧ����ȷ�˽��ն�ϵͳ�IJ���ģʽ�Լ���Դ�ֲ�״̬��������FPGA�ܹ�����ʶ��Ƕ��ʽ���ܷ��顢��Դ������ԣ����Դģʽ�����ֲ�����ѹ�ȣ������Ա���п��ܰ����ʵ�����Ƽ��ɣ��������ԴԤ���Ҫ��

��ϵͳ�ܹ�ʦ��˵�����ǽ������Ʒ�����Ϊ��ȡ���ն�ϵͳ�IJ���ģʽ��ϵͳ��Դ�ֲ�������ϵͳ�ֱ������á�˯�ߡ��ر�ģʽ��ʱ��

����Ķ�:

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������