������Ƶ�ܼ��ͱ�Яʽ��Ʒ���ܺ�

����3G�������ķ�չ�����ϼ��ɵ�·��IC�������IJ��Ͻ�������Яʽ���ѵ����豸ӵ��������Ŀѣ�IJ��Ÿ�����Ƶ���ݵ��������������ӵ��ƶ���Ʒ���û������˶�ʵ��Ӿ�����֮�У���ʵʱ��Ƶ������ʽ��Ϸ������ʽ��ͼ����ҳ������и߷ֱ�����Ƭ�����ң������ǻ������ֻ�������ȫ���ܵ�PDA����Щ���ܶ��ڲ�Ʒ����������������������Ҫ�����ã��Ӷ������г��ɹ�ҲӰ���

���ǣ�ʵ����˹��ܵ�ͼ�������ܺĶ��ܴ��������Яϵͳ���ʦ�������ս��ͼ����������Ҫ�ܼ��ļ��㣬ͬʱ����ʱ������Ҳ���ӳ���������˵���ܴ�����Ƶ���ƶ��豸�����ܹ��������ÿһ֡���н�ѹ�����롢�����ߴ粢��֮ʩ��ͼ�ι�������Ȼ������Ҫ��ÿ��30�ε�Ƶ���ظ���Щ���㣬���ܱ�֤������ƶ��豸��ʾ������Ƶ��������ʵʵ���ڵĹ������أ��Ե��ܵ�θ��Ҳ�dz���

�����߶Ը���Ƶ��Ʒ�Ŀ�����ȥ�������������������ܺġ��ӳ����ʹ��ʱ��Ա�Яʽ�ƶ���Ʒ��˵��һֱ�Ǹ��ȶ�����������ֻ����ͻ��Ŀ����Ҫһ��ȫ���ۺϵķ�������ʡ���ܡ���Я��Ʒ���ʦ��������������������ϲ�����ܼ������Ա��ڴ����ܺĺ������ܺ������涼�ﵽҪ��

�ĵ������

Ҫ����ƶ��豸���ܺĽ����Ż������ȱ������⾲̬�Ͷ�̬������������̬�ܺ��Ǵ����ܺĵ���Ҫ��ɲ��֣���Ҫ�����ھ���ܵ�й¶��������С�����ߴ��һ������Ʒ���������˾���ܵ�й¶������

�����ʦ��˵��һ�������˵ģ���й¶�������ۺϽ�ʹ�ö��ѹ����Ԫ�����Զ��ı궨�����ۺϹ����У����Ը��ݵ��ܺ����ܵ�����ѡ��Ԫ��������ѹ�ĵ�Ԫ���Լ���й¶������������ڵ�����ѹ�ĵ�Ԫ�����Ŀ���Ҫ�����ࡣ��ʱ��Ҫ���ϸ��ؿ�����һ��ĵ�·�У�����ʹ�ø�����ѹ��Ԫ�����;�̬�ܺġ������Ľ���������һϵ�в�ͬ����ѹ�ĵ�Ԫ����̬�ܺ�Ҳ��ͨ�����ܺĵ�ʵ�ֹ��ߵõ����Զ����Ż�����˴��������������������˵�Ѿ��������ˡ�

��ܺģ�Ҳ���Ƕ�̬�ܺģ����������еĽ����ͨ����������Ҫ�Ŀ��ػ���ܽ���һЩ���Ĵ������伶��RTL��ʱ���ſ��ǽ��Ͷ�̬�ܺĽϳ��õļ�����ʱ���ſ�ͨ����ѡ��عر�ʱ������������Ҫ�Ŀ��ػ���Ӷ�����ؽ��ͼ����ܼ���Ӧ����ͼ�����еĶ�̬�ܺġ�

ʱ���ſؼ���

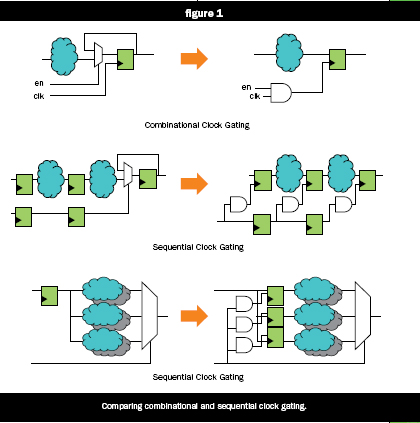

�������������͵�ʱ���ſؼ������ֱ��Ǻϲ��ͣ�Combinational����˳���ͣ�Sequential������ͼ1�����ϲ���ʱ���ſ���ֱ����RTL������ȡ��������������ʱ���ſص�Ԫ���뵽�Ĵ�����ʱ��ͨ·�С����ܺĵ�RTL�ۺϹ�����ģʽƥ��Ļ������Զ�ʶ����ϲ��͵�ʱ���ſء����ڵ��ܺ��ۺϹ����ڶ��̶��Ͽ���ʹ��ʱ���ſ�������⣬��Ҫ�ܵ�RTL��α������Լ�����ܺĵ��ۺϹ�����ͨ����RTL�����У�ͨ���ڶ�������֮ǰ�ҵ����Ե�“�����IF��”�������ҵ����Բ���ʱ���ſصĻ���ġ����ǣ���Щ���߲����ܷ�����������ʱ�ںδ���RTL�����������“�����IF������”�Ա㽵���ܺġ�����Ҫ����RTL������ڴ��������Ե�д������“�����IF������”�����ܺ��ۺϹ��߲��ܰ����Ƿ���ɽ��ܵ�ʱ���ſء�

˳����ʱ���ſ���һ�ָ�ǿ����Ż����������ڼ����ܼ���Ӧ���н����ܺĵ������Ѿ��õ���֤����ϲ���ʱ���ſز�ͬ��˳����ʱ���ſز����Ǽķ��롣�������˶������Ϊ�����з��������з������������·���ܽ������״̬�����ڵ�Ѳ�ӣ�ʶ�������Ҫ�Ŀ��ض��������粢�������õ����ݼ���ȡ�֮�������ҳ���ص����������������ֿ��ض�����

������˵����һ���Ĵ�������������ڵ�ǰ��·�����е�ʱ�����з������������������رպϲ����к���ǰһ������������������ݵļĴ����еĿ��ء��������й�ϵ������ǰ������ڶ�������д�����RTL������ǰ����ж������й�ϵ���������������ٿ��ض�����������˿����Ż��Ĵ������ڴ桢ʱ���Լ��ϲ����ĵ������ġ�

����ʱ���ſ��ܴ����Ľ���Ч���Ƿdz������ģ��ر�����������Ƶ��������Ӧ���У�����Ӧ��һ�㶼��֧�ֶ�����Ƶ��ʽ�����������ݵ��㷨������������Ƶ���IJ�ͬ��ͨ��ֻ��Ҫ�����е�һ���ֽ��н�������������������ˣ�������ʦ�ܳ����������е����й�ϵ���ͻᷢ���������������ʹ��ʱ���ſصĻ��ᡣ

����ʱ���ſ�

��ʵ��ʱ���ſط���ѧʱ�������ؼ����أ���ȫ��ʶ������п��õ�ʱ���ſػ����ȷ�����ɿ���������Щ�����RTL���룻��Ч�ض���Щ������ʱ���ſص�RTL���������֤��ȷ������Ȼ������ԭ�й��ܡ�

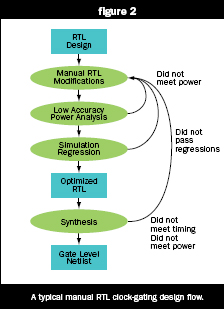

ֻ���Ͻ�������ʱ���ſص�һ�㷽������Ҫ������Լ�ȥ�鿴���룬Ѱ��ʱ���ſصĻ��Ტ�ֹ���RTL�����м��������IF���������͵�ʱ���ſ���ƹ����������ֹ�����ʱ���ſ��Ż����룬ʹ��RTL�ܺĹ��Ʒ�����������Щ�Ż�������Ч�����Ϻ�����ģ��ع�����֤����Ҫ�Ĺ��ܶ����ڡ��Ϻ��Ƕ�RTL��������ۺϣ�ͬʱ���Զ��ż��ĵ������Ľ��й����Ա�����Ƿ���Ҫ�����ʱ���ſأ���ͼ2����

����������л��������Ч�ʵĵط������ڵ�·��ʱ���ſصĻ����dz��࣬����ʹ�������ַdz����ӣ����ʦ�ܻ�����鲢��RTL���뷽�滨�Ѵ�����ʱ�䡣ͬʱ�����ڲ������е�ʱ���ſ��Ż��������ܴ����ڵ�Ч��������������һЩ���ʱ�������в���Ӱ�죬���Ի���Ҫ������ķ������õ��ϵ��ܺĵ���ơ������ֹ��������Ͷ��ܼ��͵ģ������ӳ��������ڲ���RTLģ����������Ҫ������Ϊʱ���ſ��Ż����������ô�ͳ�ĺϲ���Ч���߽�����֤�����Ի����뿪���µ�ģ����Ի�������ߣ�����֤�µ�ʱ���ſط���û��Ӱ��ԭ�еĹ��ܡ������һ��������Ȼ������������Զ�����

��RTL������������ܺ��Ż�����

�ڲ����µ��ܺ��Ż�����ʱ������Ŷ�Ҫ��ʱ���ż����ؼ����ǡ���һ���¹��ߴ����ĵ��ܽ�ʡ���Բ��䲢�ۻ��������ܺ��Ż������ϣ���һ��dz���Ҫ���ڶ���Ϊ�˱���ѧϰ���߹��������ӽű������������¹���Ӧ����ʹ�ñ����ļ���ʽ�������ܹ��������е��������֮�С��������dz���Ҫ��һ�����¹���Ӧ���ṩһ��ȫ��Ľ��������������������е������ط����������⡣���磬�Զ�ʶ��ʱ���ſػ����Ǻ����õģ������������߲��������Ż�����RTL���롢��ȫ����֤����ԭ�й��ܶ�û��ʧЧ�������ͻ�������ʴ�����������

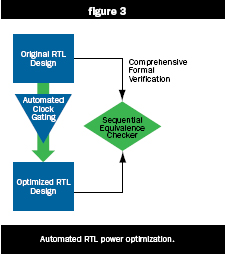

�Ͻ��������Զ�����ʶ����RTL����в��벢��֤����ʱ���ſص���ҵ��������Ѿ������ˣ�ͼ3����ʹ�������Զ�����ʱ���ſغ���֤����Ϊ��Ƶ�ܼ��ͱ�ЯʽӦ�ô����˾�Ľ���Ч����

��Щ���ܰ�����Calyptoϵͳ��˾��PowerPro CG��ʱ���ſأ���SLEC CG�С�PowerPro CG��һ���Զ�����RTL�����Ż��������������֤�����Դ����ϸߴ�60%�ĵ��ܽ�ʡ��ͬʱ�����������Ӱ���С����û��Ӱ�졣SLEC CG��һ�����е�Ч���ߣ���������֤����ʱ���ſص��Ż�����Щ���߲��������еĵ��ܺ���ƹ����������ǿ��Է���RTL����е�������Ϊ��ʶ���ʱ���ſػ��ᣬ�����еĹ��߸�ǿ�����ǿ��Զ�ȡ���ġ����ۺϵ�Verilog��VHDL RTL���룬�Ӷ�����Ƕ�뵽���е��������ȥ��

���⣬���ɵ��ܺ��Ż���RTL����ͬԭ���Ĵ��ж���ʱ���ſ�����RTL�����һ���ġ��ܺ��Ż���RTL���뻹Ҫʹ����������Ч���߽���ȫ�����֤����ȷ��û�д��������ϵĸı䡣�ܺ��Ż���RTL��ƿ���ֱ�ӽ�����ܺ��ۺϣ��Ա�ӵ�����ε����Ż������ĸ������ơ�ͨ�������ʦ�ӷ��ӵ���Ʒ������ֹ���RTL�����Լ���ʱ��ģ����н�ų���������Ч�ʺͽ���Ч�����õ���������

����

�ڼ����ܼ������ܺIJ������ܺ��Ż�����������������������м�������ʱ���ſص���ƹ����У������Ż���һ���ؼ��������ʦ��������ڴ�����Ƶ��ͬʱ����������������ġ�������ǰ���Զ�������ʱ���ſؽ�����������ʦ���Խ�ʡ������ܣ�ͬʱ������е��ֹ�ʱ���ſط��������Ч�ʡ�

����Ķ�:

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������