ʹ�������������ƶ���ƵĹ���

��ǰ���ƶ������Ŭ���ڸߺ���(power-rich)�Ĺ����Ժ����������������֮��ȡ��ƽ�⡣���Ľ�̽���ڻ�ϵ�ѹ������ƶ�����У���ϵ�ѹ��ƽ������ICC ��Դ������������ν����ġ�

��Icct ���������ڽ���

Ŀǰ���������Я�豸�����ж����Դ�죬��������ߵ�ƽ(VIH)���ڵ�Դ��ѹ(VCC)ʱ���Կ��ܲ����������ġ��������ѹΪ��Դ���ƽ(VIL = Gnd �� VIH = VCC)ʱ��CMOSһ����м��͵ľ�̬ICC��й©�����������ƶ�Ӧ��������������ѡ��������������VIH < VCC���ᷢ��������������뼶��PMOS �� NMOS����ܿ��ܾ��ڲ�ͬ��‘��ͨ’����ʱ���������������״̬�ڼ䣬��̬����ICC���ӣ�����һ����VCC �� Gnd��·����������ӵĵ�������ΪICCT���������������ѹ�ƽ���ֵʱ�ĵ�Դ������ͼ1���������������

�����ѹ���ڵ�Դ��ѹVccʱΪʹ��CMOS�ŵ�·������״̬����ʱICC�������͡�

�ڻ�ϵ�ѹ����£���Vin < VCC��ICCT�������֣�����Ҳ��֮������

ͼ1�����ź������ѹ����

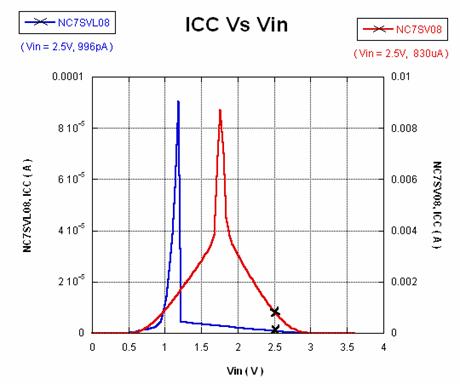

һ����CMOS �ŵ�·������У������ѹ��ֵ�������л���ΪVCC/2�����������װ뵼��ĵ�ICCT�ŵ�·����ר�е������ѹ��ƣ��ɽ���������ֵ��ѹ�����������ѹ��Χ��ͬʱ��Ӱ����Ч���͵�ƽVIL����ǰ�������������ѹΪ0V �� VCC ʱ��CMOS�ŵ�·�ĺĵ������ͣ�����Ʒ�����ֲ�ͨ����ע���������µ�ICC����ˣ�ϵͳ�����Ա��VIH ֵС��VCCʱ����ICC�������������Ϊ���ȡ������ͼ2��ʾ��һ��������Ƶ�����ṹ���ŵ㡣�����VIN - ICC ͼ�Ƚ���һ����CMOS��������(��ɫ����)��һ����ICCT��������(��ɫ����)����̬�����ɻ���DC���ʹ�ʽ������P = ICC * VCC���ڱ����У�����VIH Ϊ2.5V����CMOS�ŵ�·����Ĺ��ĵ���3.0mW (3.6V x 0.83mA) ������ ICCT�ŵ�·�Ĺ���ֻ��0.003mW (3.6V x 0.99uA)��Ҳ����˵������Low ICCT ��������̬���Ľ�����100%��

ͼ2��ICC -VIN �������� (Vcc = 3.6V, VIN = 2.5V)

ICC����������ʮ����Ҫ����Ϊ�����������������ľ�̬���ġ����װ뵼���ר�е�ICCT����ṹ����ICCT ���������ڼ������䷶Χ����ͼ2��ʾ��

|

| ICCT ���� |

| |

VCC | VIN | �� CMOS �ŵ�· | ��ICCT �ŵ�· | ���� |

3.6 | 3.6 | 5.1 nA | 1.5 nA | 70% |

3.6 | 2.5 | 830 uA | 996 pA | 100% |

3.6 | 1.8 | 7.0 mA | 2.7 uA | 100% |

3.6 | 1.5 | 2.8 mA | 3.5 uA | 100% |

2.5 | 2.5 | 1.2 nA | 983 pA | 23% |

2.5 | 1.8 | 21.4 uA | 39.2nA | 100% |

2.5 | 1.5 | 417 uA | 577 nA | 100% |

1.8 | 1.8 | 835 pA | 656 pA | 21% |

1.8 | 1.5 | 2.6 nA | 713 pA | 73% |

1.8 | 1.2 | 2.6 uA | 4.6 nA | 100% |

��1����ͬVIH�����µĽ���DZ��

��1�Ƚ��˲�ͬVCC / VIN �����µ�ICCT��Դ���������ӱ��пɿ��������װ뵼��ĵ�ICCT�ŵ�·���кܴ�Ľ���DZ�����ڻ�ϵ�ѹϵͳ�У����õ�ICCT�ŵ�·�������ŵ�·��صĹ��Ŀɽ����������

��ο��±��г��ĵ�ICCT�ŵ�·���������������Ҫ�����ṩ����Ĺ��ܡ�������Ӧ����ǰ�����۵��������������ֹ��Ĺ���ʱ���û������ñ����������ֱ�Ӽ��ؽ����滻��