����ͬ������SEPIC���˽ṹʵ�ָ�Ч�ʽ�ѹ/��ѹת����

�����г��Ը�Ч��ͬ��DC-DCת�����������ڲ�����������Щת�������Խ�ѹ����ѹģʽ�����������Խ������ѹ���ͻ������������ȶ���ѹ�����Ҿ��нϵ͵ijɱ��ͽ��ٵ�Ԫ������������SEPIC�����˳������ת������Ҳ��ΪZetaת��������������֧�ִ˹��ܵ����ԣ�ͼ1�������乤��ԭ��������˫ͨ��ͬ�����ؿ�����ADP1877��ʵʩ�������з����������˽����ڱ�Ӧ���е��������ԡ�

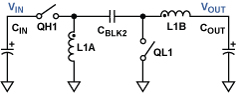

ͼ1. ����SEPIC���˽ṹ

��������QH1�ʹμ�����QL1��������ڵ�ͨʱ���ڣ�QH1��ͨ��QL1�Ͽ�������������·����������ͼ2��ʾ����һ��·���Ǵ�����˾����������ء������������(CBLK2)��������(L1B)���أ�����ͨ������������ˡ��ڶ���·���Ǵ�����˾����������ء��ػ����(L1A)�͵���������ˡ�

ͼ2. ��������ͼ��QH1�պ���QL1�Ͽ���

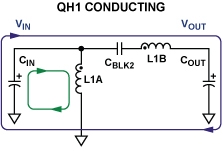

�ڹض��ڼ䣬����λ�øպ��෴��QL1��ͨ��QH1�Ͽ����������(CIN)�Ͽ��������������������������·����������ͼ3��ʾ����һ��·���Ǵ������о������ء��غʹμ��������������С��ڶ���·���Ǵӵػ���о�������������ݡ��μ��������صػ���С�

ͼ3. ��������ͼ��QL1�պ���QH1�Ͽ���

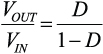

Ӧ�õ�з���ƽ��ԭ���͵��ݵ��ƽ��ԭ����������÷���ʽ1���涨�ľ���ֱ��ת���ȣ�����DΪת������ռ�ձȣ�һ�����ڵĵ�ͨʱ�䲿�֣���

| (1) |

��ʽ���������ռ�ձȴ���0.5������˽���ýϸߵĵ��ڵ�ѹ����ѹ�������ռ�ձ�С��0.5�����ڵ�ѹ��ϵ�����ѹ��������ɷ����õ�������ؽ����������ϵͳ�У������������(CBLK2)�ϵ���̬��ѹ����VOUT������������(L1B)��ֱ������ֵ����IOUT�������ػ����(L1A)��ֱ������ֵ����IOUT × VOUT/VIN��������������ݻ����ṩVIN��VOUT�ĸ�ֱ�������������·����ʱ�������Ժ����á�

��������ʾ������SEPIC�е���������������ģ����ڸ�����������迹��������ϵ͵ķ��ֵ�����ѹ�Ʋ����������ʹ�ý�С���ϱ��˵�������ݣ����֮�£��ڷ���������������˽ṹ�У�Ϊ�˴ﵽͬ�����Ʋ�Ҫ����Ҫʹ�ýϴ��Ұ���ĵ��ݡ�

ͨ�����μ�����(QL1)��һ�������ʶ����ܣ����������������˽ṹ�ķ�ֵЧ�ʡ�Ȼ��������ADI��˾˫ͨ��ͬ�����ؿ�����ADP1877������¼����һ��ͨ����������˫��MOSFET��Ϊ�μ����أ��������һ��“��ȫͬ������”�ķ���SEPIC����������ֵЧ�ʽ������ߣ�ͬʱ���Խ��������������1 A��ת�����ߴ�ͳɱ���

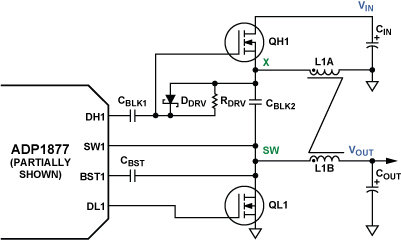

ͼ4��ʾ��ȫͬ������SEPIC���õĹ��ʼ���������ADP1877ʵ�֣�ֻ��Ҫ����С�͡����۵Ķ���������CBLK1��DDRV��RDRV�����书�Ŀ��Ժ��Բ��ơ�

ͼ4. ͬ������SEPIC�Ĺ��ʼ�������ADP1877��ͨ��1ʵ��

����SEPIC��������̬������ͼ5��ʾ��ͨ��1���ؽڵ�SW1������¼ͼA����VIN + VOUT����ͨʱ���ڣ���0 V���ض�ʱ���ڣ�֮���л�������ɱõ���CBST���ӵ�SW1���Ա��ڵ�ͨʱ���ڽ�ԼΪVIN + VOUT + 5 V�ĵ�ѹʩ���ڸ߶��ڲ����������Ծ��ϵ�죨BST1���ţ��߶��������������DH1���ţ����Ӷ���ǿ��������N����MOSFET����QH1����λ������DDRVȷ����̬����ڼ�CBLK1�ϵĵ�ѹԼΪVOUT + VFWD(DDRV)���õ�ѹ�ο�ADP1877��DH1���ŵ�QH1դ���ĵ�ѹ���ڹض�ʱ���ڣ���X�ڵ��ѹԼΪ–VOUTʱ��CBLK1�ϵĵ�ѹ��ֹ�������ز�����������ֵ��դ��-Դ����ѹ��

ͼ5. ͬ������SEPIC�����벨��������������

ADP1877����������Ծģʽ��ʹ��ʱ�����Խ��Ϳ������ʣ�ֻ��������ṩ���Ա��������ѹ�ȶ����������Ӷ����С����ʱ��Ч�ʣ����դ����ɺͿ�����ġ���ͬ������SEPIC��ͬ����ѹ���˽ṹ�о�����ʹ�ܴ�ģʽ��ͼ4��ʾDC-DCת����·ֻ��Ҫ˫ͨ��ADP1877��һ��ͨ���������һͨ������������һ�����˽ṹ��

�����Ϻ������������

ͼ4�У����ʵ��L1A��L1B��ʾΪ�˴���ϡ����������˽ṹ�У���ϵ�е�Ŀ���Ǽ��������ѹ�͵�е������Ʋ���������߽ϴ���ܱջ���������һ���ֽ��Դ˼���˵����

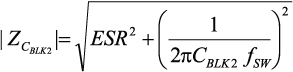

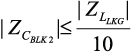

��Ȼ��Щ��л�����ϣ�������ϣ�����̫���������ڽ�һ������Ĵ�������ͨ����о��������һ�����顣Ϊ�˱�����һ�㣬���������ϵ�е�й©���(LLKG)����ѡ���ʵ��������������(CBLK2)��ʹ���临���迹�ķ�ֵΪй©����뵥���������(DCR)�ĸ������迹��1/10���緽��ʽ2��3��4��ʾ��������һ��ϵ��Ƶ�·����ʹ�����о����������������ϵ͡�й©��п��Ը�����ϵ�������ֲ����ṩ�����ϵ�����㡣

| (2) |

| (3) |

| (4) |

�����ȽϺ�Ϊ1:1����Ϊ���ڸ���ˮƽ�������ѹ�Ʋ�����ʱ������ֻ��Ҫ������������е�һ��1������ʹ��1:1����������ȣ������������ñ����еķ���ʽȷ������

С�źŷ����ͻ�·����

����SEPICת����������С�źŷ��������˱��ĵķ�Χ�������������������ԭ����������������ѧ�����塣

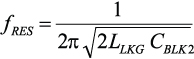

���ȱ������г��Ƶ��(fRES)ʱ�����ิ���迹�������Ա����Ŀ�꽻ԽƵ�ʵ����ޡ�����н���ʱ����Ƶ�ʽ��ͣ����½ϴ���ܱջ������������͡�

| (5) |

�ڴ�Ƶ��ʱ��������300°������“��Q”��λ���͡�Ϊ�˱���ת�������������ط�Χ����λԣ��ƫС�����⣬Ŀ�꽻ԽƵ��(fUNITY)ӦΪfRES��1/10����г���������Ҫȡ����������ص������ϵ�е�ֱ�����衣�ڽ�С�̶��ϣ����ỹȡ��������������ݵĵ�Ч��������(ESR)����MOSFET��QHl��QL1���ĵ�ͨ���衣��ˣ���������ص���ı�ʱ���ջ����ݺ����������ڸ�Ƶ��ʱ�������Ա仯Ҳ����Ϊ�档

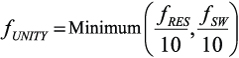

���ϵ��ͨ������һ���ܹ���ȷ���ƵIJ��������Ӧ��Ŀ�꽻ԽƵ������Ϊ��fRES��10����ֵ������fRESС�ڿ���Ƶ��fSW������fUNITY�����ʵ�ʱ������ʹ�ñ�“II��”����——���������һ����㡣

| (6) |

ͼ6��ʾͬ������SEP

����Ķ�:

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������