FPGA�뵥Ƭ��ʵ�ֵ�Ƶ����ʽ��λ������

ժҪ���������AVR ATmega128��Ƭ����Altera��˾��Cycloneϵ��EP1C3T100Ϊ���ĵ�ϵͳ��Ʒ���������������ʽ��Ƶ��λ�����ǵIJ���ԭ���Ͳ������������ķ�������Ҫ������ϵͳ����Ӳ����ơ�ʵ���������˷�����Ƶ���λ�ǶԵ�Ƶ���Ҳ��ź�ʵ�־�ȷ��Ƶ�Ͳ���λ����д����ٶȿ졢�ȶ��ɿ������ȸߵ��ŵ㡣

�����ؼ��ʣ�������λ��;��Ƭ��;FPGA;���;Ƶ��;��λ��

��������Ʋ���MCU��FPGA���ϵ�ϵͳ��������AVR��Ƭ��ATmega128��Altera��˾��Cycloneϵ��EP1C3T100Ϊ���ģ���ַ��Ӹ��Ե����ƣ���AVR��Ƭ���Ƚ���RISC�ṹ��ǿ�������㡢���ƹ��ܣ�Altera��˾��FPGA�����ٶȿ졢��Դ�ḻ�Լ��ױ�̵��ص㣬������ƣ��˷�������λ�Ǿ߱��ٶȿ졢�ȶ��ɿ������ȸߵ��ŵ㣬��������ʵ��“���ܻ�”��“�Զ���”��

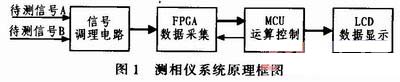

����1 ϵͳ�������

����1.1 ���������ıȽ���ѡ��

����Ŀǰ��λ�����ķ�����Ҫ�����֣�

����1)DFT���෨���������ź�ͨ��A/Dת���õ�f(n)��f(n)����ɢ����Ҷ�任�ó���ɢƵ��F(k)��f(n)��F(k)Ϊ����Ҷ�任�ԣ�ͨ������õ���·�źŵĻ�����λ���Ӷ��������λ�DFT���෨�ľ���������ADC�IJ������ȣ���Ҫ����ADC���źŽ��й������������������ӣ�����ͨ���ɼ����ڼ������ʵ������������������ҪӦ���ھ���Ҫ��ܸߵij��Ϻ����������С�

����2)���������෨ ����·ͬƵ�������źž����ź����ε�·��õ������źţ������źž����������õ���·�����źŵ���λ���źţ��ù̶�Ƶ�ʵIJ������������䲢�������Ӷ��������λ����������෨��ҪӦ����Ҫ��һ���ľ��ȣ�������Ƶ�ʲ���̫�ߵ�ʵʱ��Ҫ���ǿ�ij��ϣ�����ʵ�����ֻ����Զ�������Ƶ������λ���ʺ�������������

�������������෨�Ļ����㷨�������Ҳ����κ�ķ����ź�Ƶ��Ϊf������ΪT��������������ΪTC������һ�������ڶԲ����������Ϊ��n���ź�Ƶ��f=1/T=1/nTC��ͬ���ķ����������ͬƵ���Ҳ����֮���ʱ���Ϊ��t�������źŵ���λ���θ=��t·360°/T��

����1.2 ϵͳ������ȷ��

������ϵͳ����������֪��������Ҫ�ɼ������㼰��ʾ�����ǵ�Field Programmable Gate Array(FPGA)���ɶȸߡ�I/O��Դ�ḻ���ȶ��ɿ���ѡ����ش���ΧԪ�����٣��������۸��½������ƣ��Լ�MCU���õ��˻��ӿں�������ƹ��ܣ����Ա�ϵͳ��MCU��FPGA���Ϲ��ɲ�����塣FPGA����ɼ���Ƶ�Ͳ���λ��������źţ�MCU�����FPGA�ɼ������ݣ���������ź�Ƶ�ʺ���λ���LCD����ʾ��

�������ԣ�ϵͳ��4��������ɣ������źŵ�����·��FPGA���ݲɼ���·��MCU����������Ƶ�·��LCD������ʾ��·����ͼ1��ʾ��

����2 �������ķ���������

������λ�����ǵ�������ƣ�����Ҫ�к��ʵIJ���������ϵͳʵ�ַ���������Ҫ���ط�����������ԭ���ȷ�������ķ�����

����1)���ʱ��Ƶ��(�����ݲ����ź�)��Ӱ����ȷ������λ�����ǵIJ�Ƶ��ΧΪ20 Hz��20 kHz����λ��ķ�ΧΪ��θ=0°��359.9°����λ�����ʾ�ֱ���Ϊ0.1°��Ҫ�������λ�ľ������≤2��

��������Ƶ��20 Hz≤f≤20 kHz��������50μs≤T≤50 ms��

����T=50 μs���������ȡ0.1°��2°��

���������ʱ���ź����ڣ�0.1°x50 μs/360°≤TC≤2°x50 μs/360°����1/72(μs)≤TC≤1/3.6(μs)�����Եó����ʱ��Ƶ�ʣ�

����3.6 MHz≤fC≤72 MHz��

����T=50ms�ڶ�TC=1/3.6(μs)������������������ֵNmin=180000≤218;��TC=1/72(μs)������������������ֵNmax=3600000≤ 222��

��������ƿ���MCU�ļ��㼰��Ƶȡ���źŵķ��㣬���ʱ���ź�Ƶ��fC=20 MHz�������������<1°��FPGA��20 MHzʱ���ź������¶Դ����ź����ں���λ��Ӧ��ʱ�����м�����FPGA�����Ķ���������λΪ20 bit�����Ա�֤�����ľ��ȡ�

����2)�����źŵ�����·�����Ư�Ƶ�Ӱ�������������źŵ�����·��Ҫ�����ǰ������ź����α任�ɾ��β���ͨ�����ù���Ƚ�������ʩ���ش�������

��������Ƚ���������λ�������ܻ����������ź�������λ����ʱ����ѹ�Ƚ������ڷŴ��������κ�ľ��β��ڱ��ػ����������ʹϵͳ�����в�����Ҫ�������ֶ��������Բ���ʩ���ش�������Ϊ�˱�֤�����ľ��ȣ�ʩ���ش����������������������һ����·�����źŷ��Ȼ�����ȣ���������ƽҪ�����ӽ���

����3)���κɱ��صĶ��ͳ̶ȵ�Ӱ���������źž������κ�����ľ��������ź�ֱ����FPGA����FPGA����������ȡ�ȶ������������źţ��ͻ�ʹϵͳ�ľ����ܵ��ܴ�Ӱ�졣����Ҫ���������κ����ز���������ɵġ�Ҫ��������⣬һ��ѡȡ���нϴ�ѹ���ʵ������������ڱȽ����ĺ�˼�һ���ֵ�·�����������źŵı��ء�

����4)�е�Ƶ�������ȵ�Ӱ������������20 MHz���ݲ����ź���ѭ�����������źŵ����ڼ���λ���Ӧ��ʱ�����ȴﵽ0.05 μs��20λ�������ĵ�λ��0.05μs�����ñ����ź�ˢ�²���������ʵ�ָ�Ƶ���������Ƶ�ٲ�����ʱ�������ȷ�ɿ���������FPGA����ΪMCU�ṩ�ȶ������ݡ�

����3 ϵͳӲ����·�����

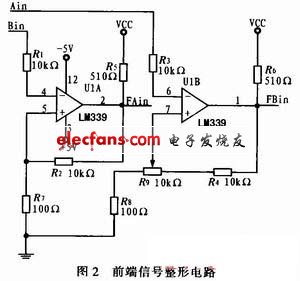

����3.1 ǰ���źŵ�����·�����

����ʩ���ش�����(���ͱȽ���)��Ȼ���Ժܺõ������Ƚ�����������Ķ���������������źź������źŴ�����λ������·�����źŵķ��Ȼ������������ʩ���ش�����������ƽ�ֺܽӽ�����ʩ���ش������������λ���Բ���ϵͳ������Ӱ�졣

��������LM339�ڲ���4�������ĵ�ѹ�Ƚ������õ�ѹ�Ƚ������ص��ǣ�ʧ����ѹС������ֵΪ2 mV;��Դ��ѹ��Χ����˫��Դ��ѹΪ±1��±18 V;�ԱȽ��ź�Դ���������ƽϿ���ͬ��ͷ�������˵�ѹ������10 mV����ȷ������ܴ�һ��״̬�ɿ���ת������һ��״̬��������൱��һֻ���Ӽ��缫����ľ��������ܣ���ʹ��ʱ����˵�����Դһ�����һֻ���衣�������ѹֵ�����ĸ��Ų������ز�AU�������ѹ��ֵ�ͽ����ȶ��ġ����������Լӿ�Ƚ�������Ӧ�ٶȡ����ڳ��ͱȽ����ӵ���������ǿ��Զ�ȵ�·�еļ������ǿ�ö࣬���Կ�������ڵ�·������϶��������Լ���ͨ�����ڵ�λ����ʹ����ʩ���ش�����������ƽ������ȣ���֤�����·����λ���������������·��ͼ2��ʾ��

����3.2 ϵͳ������·���

�����Ե�Ƭ��Ϊ���������λ�ǣ����侧��Ϊ24 MHz����Ƭ��C/T�ļ������Ϊ1����������Ϊ±0.5 μs����������Ϊ360°x0.5 μs/50μs=3.6°�����ԣ��������ź�Ƶ�ʺܸ�ʱ�����������Ҫ��

��������Ʋ���AVR��Ƭ����FPGA���ϵķ�����FPGAʵ�����ݲɼ����������źŵ�Ƶ�ʺ���λ������Ӧʱ���ת��Ϊ���������ݴ�����Ƭ��;��Ƭ����FPGA��ȡ���ݣ��������㡢ת�������ݴ������������źŵ�Ƶ�ʺ���λ����LCD����ʾ��

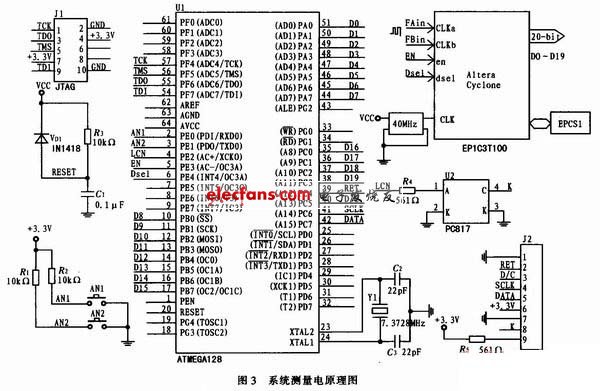

��ϵͳ��ԭ��ͼ��ͼ3��ʾ��MCU����ATMEL��˾��AVR��Ƭ��ATmega128�������Ƚ���RISC�ṹ�������ָ����һ��ʱ����������ɣ���32��8λͨ�ù����Ĵ�����������ƼĴ������˷���һ�㵥Ƭ����һ�ۼ������ݴ���������ƿ������128 KB��ϵͳ�ڿɱ��Flash��4 KB��EEPROM�Լ�4 KB���ڲ�SRAM����ѭJTAG���ı߽�ɨ�蹦�ܣ�֧����չ��Ƭ�ڵ��ԣ���ͨ��JTAG�ӿ�ʵ�ֶ�Flash��EEPROM����˿λ������λ�ı�̡�

����FPGA����Altem Cycloneϵ�е�EP1C3T100������оƬΪEPCS1��VHDL���ܳ���ȫ���������.sof��.pof�ļ������õ�����ΪByte-Blaster II��[Mode]��ѡ��“JTAG”Ϊ��.sof�ļ����õ�FPGAоƬEP1C3T100�У����ڵ���;[Mode]��ѡ��“Active Serial Programming”Ϊ��.pof�ļ����ص�����оƬEPCS1�У�ϵͳ�����ϵ�ʱ�������С�

����LCD����HTM12864��Ϊ128x64�������ݴ���Һ����ʾ���������ͨ�������ܵ����ơ�

����ATmega128��EP1C3T100��Ƹ��Ե�JTAG�ӿڡ�ͼ3�����ATmega128��EP1C3T100�Ľӿ�D0��D19��EN��Dsel��LCN;ATmega128��HTM12864�Ľӿ�RET��D/C��SCLK��DATA;EP1C3T100�������ź�FAin��FBin��66 MHz�ⲿ��Դ��������оƬEPCS1��4 ϵͳ���������

����4.1 FPGA���ݲɼ�VHDL�������

����FPGA���ݲɼ���VHDL�����������Altera QuartuslI��������ƽ̨��ʵ�鿪��ϵͳ����ɵġ�������Ʋ����Զ�����(up-to-down)����Ʒ�����FPGAϵͳ��ģ�鹹����ͼ4��ʾ�������źŷ���ģ�����ʱ���ź�Դ�ķ�Ƶ�������õ�CLK=20 MHz;�����źŲ���ģ���ڿ����źŲ���ģ�������բ���ź�Tk��ʱ�������ź�Tcr�������£���������ź����ں���λ������;����������ȡģ���ڼ����ź�JXc�ͼ�����ȡ�ź�Lad�������£��������ʹ���ź�EN�����������ź�Dsel�����·ֱ�������ں���λ�����ݣ���MCU���㴦����ʾ��

����FP

����Ķ�:

- ...2015/09/24 18:00��FPGA��Դ���

- ...2012/10/29 10:29�����ϸ�����������FPGA,ʵ�ֽϼ�WLAN����

- ...2012/10/22 13:14���˽�LabVIEW FPGA�����������Ƶ��������������

- ...2012/09/24 13:59��NI PXI���FPGAʵ�ֽϼ�WLAN������֧��802.11ac

- ...2012/09/17 14:04���˽�LabVIEW FPGA�����������Ƶ��������������

- ...2012/08/13 13:22��ʹ��LabVIEW��FPGA������һ���Զ���������������ϵͳ

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������