�����͵���DDR I��II �� IIIʱ�Ӷ�������

���ߣ�Min Jie Chong

�����Ƽ���˾

�洢���������/��֤��Ʒ����

����

���� DDR��˫��������ͬ����̬����洢�����洢�����������ݴ�������Ѹ����������ͨ������Ϊ����ʦ���ٵľ���ս���Ӹ����Ͻ�����ͨ�������Ǵ������㿪ʼʵʩ�����������Ҫ������֮һ��ʱ���źŵĶ������ܡ�DDR �ӿ��ϵ�ʱ�ӴӴ洢���������䵽 DDR оƬ������ DDR ϵͳ�����������źţ�����ѡͨ�źš������źš���ַ�źź������źţ��IJο�����ˣ�ӵ�����õ�ʱ�Ӷ�������������Ҫ����Ϊʱ���ϵĶ�����ת�Ƹ������źš������һ��ʼʱ�ӵĶ������ܾͺܲ��ô�����ź��ϵĶ�������Ҳ��dz����ԡ�

�������Ӱ�� DDR ϵͳ�����ܣ���������Ӱ������ƶ�����Ϊ����ʹ���ص�λ�û��źŵķ��ȷ�����λ��ʹ��ƫ������λ�á�����Խ��Ե�����ƫ��������λ�þ�ԽԶ���ڷ�����λ���ϣ�DDR ϵͳ���ܲɼ���������Ϣ���Ӷ����������ϵͳ�ı��������ʡ����գ�ϵͳ�����������������ڸ���� DDR �ٶȣ��䴰����Чʱ�����̣�ʹ��һ������Ӷ���ʱ��ʹ��С�Ķ���Ҳ�ᵼ���������⡣

����ʱ�Ӷ������ڻ�ͨ�������Ҫ����� JEDEC�����ӹ�����Ʒ�չ����Э�ᣩ�ѹ涨��ʱ�ӱ������ص������������������Ŀ����ȷ������������������Χ���ڣ����� DDR ϵͳͨ�žͲ����жϡ����ոü���ָ�꣬����ʦ�����ٵ���ս��������ȷ��ʱ�Ӵ��ڶ�������ָ�귶Χ�ڣ���Ҫ��ʱ�Ӳ�����Ҫ��ʱ���е��ԺͲ��Ҷ���Դ�����Ľ��ص����һЩ��ʾ�����п��õĹ��ߺͷ��������ǿ���������ʦ����ִ��ʱ�Ӷ��������Լ����Զ������ϡ���Щ���ߺͷ�����DDR 1��2 �� 3 �����á�

�Զ�ʱ�Ӷ�������

��һ�����Ķ������Լ���ָ��ʹ�ö�ʱ�Ӳ��εIJ����ͷ����dz���ʱ������Ҫ���ǣ����������зdz������Ҫ��DDR2 ����ָ��D�DJESD79-2D Ҫ��ʾ�����ܹ��� 200 ��ʱ�������ڷ���������ڼ䶶��������һЩ���������� tJIT(cc)��tERR(2per)��tERR(3per) �� tJIT(duty) �ȡ���Ȼ����ָ����û���ἰ�����Ƕ�������Ӧ���ڴ�����ʱ���������ظ����У�ͨ��Ϊ 5000 ��ʱ�����ڣ���ȷ���ȶ��ԡ�����������ЩҪ������Ȼ�����ٷdz����ص�����

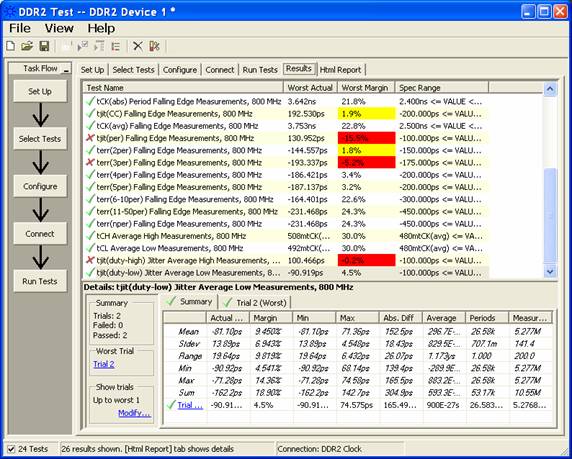

���˵��ǣ���Щʾ�����ṩ�� DDR һ���Բ�����������Щ�������Ը��� JEDEC ����ָ���Զ�����ʱ�Ӳ����ͷ���������Ҫ���ľ��ǽ�ʱ���ź�����ʾ������ѡ��ʱ�Ӷ������ԣ�Ȼ��ִ�в��ԡ��������������� JEDEC ����ָ����бȽϣ�������ÿ�����Գɹ���ʧ�ܵ��������ͼ 1 ��ʾ���������Զ���������һ�������ǿ�����һ�νϳ���ʱ�������ж������ԣ��Ա����������Ҫ������ʱ�����ڡ���ЩӦ����������ֶ����в����ĸ�����ʹ�����Խ�ʡ����ʱ��;�����

ͼ 1��DDR2 Ӧ����ʾ��ʱ�Ӷ������ԵĽ������ɫ��ʾʧ�ܵIJ��ԣ���ɫ��ʾ�պóɹ��IJ��ԡ���ˣ���ʱ��δ�ﵽ JEDEC ��������ָ�꣬��Ȼ��Ҫ����������

ʹ�ö������뷨����ʱ�Ӷ�������

���ڣ������Զ����������������dz������������ͼ 1 ��ʾ�����������ʱ�Ӷ������ϣ�����ֻ�����أ������ִ������ʱ��������⽫��dz��鷳����Ϊ������Դ�����Ƕ��ġ��������Ѹ����С������Դ�ķ�Χ,�������ζ�������뻨�Ѻü����µ�ʱ��������ȷ������Դ�����ֱ��������롣

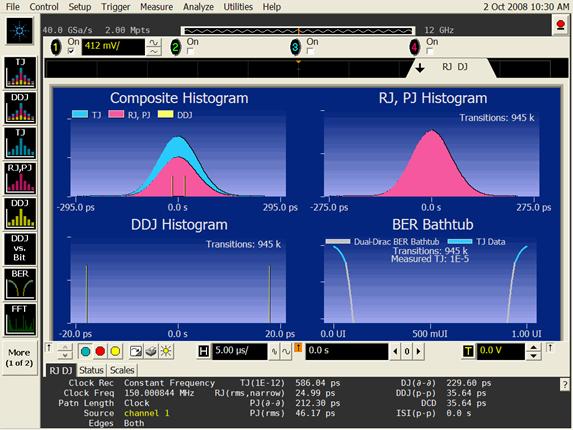

Ψһ��ϣ����ʾ�������и��ֶ������Է���������Ҫ��һ�������ǽ�ʱ�ӵ����嶶����TJ������ɲ�ͬ�Ķ����ɷ֣���ͼ 2 ��ʾ�������ַ����dz���Ҫ����Ϊ����ܹ�֪��ʱ���ϵĶ�������,�Ϳ�������ȷ������Դ�����⣬�������Բ���ÿ���������͵ķ��ȣ��Ӷ����о�����������ֶ����Ķ���Դ��

��Щ���͵Ķ������Դ� TJ �з��������ʱ���ϵ����������RJ����������е���ԴԪ��������������ɵģ����Dz�ȷ���ģ����Ҷ���������û�б߽����Ƶġ����������ڣ������ϵͳ���¼��������������ϵͳ��Ҫ�ڷdz��ߵı��������������¹�����Ҫȷ������һ��Ԫ��������Ĺ��ϣ�������ʹ��ʾ����̽ͷ����Ԫ�����������Ȼ��ʹ�ö������뷨�鿴ÿ��Ԫ������������ RJ ��С�����ҵ� RJ ��������Ԫ����֮��������ʹ��һ���������õIJ��������������ȻҲ��������ʵ�����������õIJ����������ɵ� RJ ���ر�ࡣ����������£������ܱ����������������Ѱ��һ���������õ�Ԫ���������� RJ ���ܡ�

��һ�බ����ռ�ձ�ʧ�棨DCD��������ȷ���ԵĶ����������б߽����ơ���������ԭ���Dz�����֮��ĵ�ѹƫ�û����ź�·��֮���Ť��ʧ�䡣��ѹƫ�������ź�·��֮����迹ʧ��͵�ѹ��ƽ�IJ�������ġ�Ť��ʧ������Ϊһ���ź�·���������߹�������ģ���ᵼ�� DCD���������ڴ洢�������͵�·����ư�ͼ�н����Щ���⡣

���ڶ�����PJ�����������ʱ���ź�����ϵ������ź�Դ���ظ��ź�Դ����ġ���Ҳ��ȷ���Եģ������б߽����ơ����� PJ ����Դ�����ǿ��ص�Դ�����������ȷ�� PJ Դ�ķ���������һ�������ۡ�

����������ɲ�ͬ�ɷ֣�����������С���ⷶΧ��ͨ������ÿ�බ���Ĵ�С�������������ֹ�����ϵ����ȼ���

ͼ 2��TJ ������ɲ�ͬ�Ķ����ɷ������� RJ��PJ �� DCD��֪�����������ͺͷ��ȿ���������С����Դ��Χ�������������ֹ�����ϵ����ȼ���

ȷ��Դ���ڶ�����PJ��

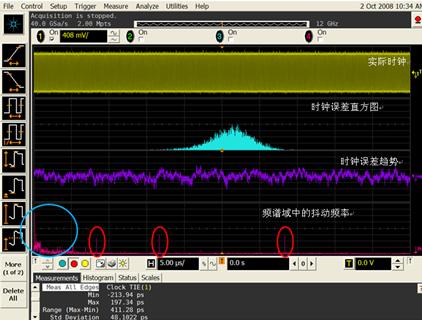

ʱ������TIE�������������ṩ����� PJ �������ù������Ȳɼ�ʵ�ʵ�ʱ�ӣ�Ȼ��ͨ����ʵ��ʱ��ȡƽ��ֵ�����ɲο�ʱ�ӣ�����ʹ�òο�ʱ�����ڼ�ȥʱ�Ӳ��ε�ÿ�����ڣ�������ʱ��仯��ʱ���������ͼ����ͼ 3a ��ʾ������ʱ��������ư���ʵ��ʱ�ӵ�ʱ����Ϣ��

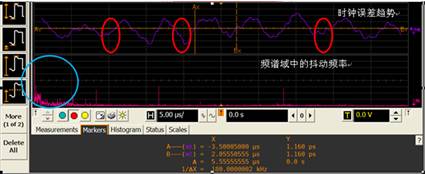

��ʱ���з���������ƿ��ܷdz����ѣ���˿��Զ�ʱ��������ƽ��п��ٸ���Ҷ�任��FFT�����Ա���Ƶ���в鿴��������ͼ 3a �У����Թ۲쵽Ƶ���ϵļ���źţ�����ʾ��ʱ����ϵĶ�����Ƶ�ʡ�Ƶ�ʼ���ź�Խ�ߣ���ɵĶ���Խ�������Թ۲쵽�� 3 ��ͻ���ļ���źţ��ں�ɫԲȦ�У������ڼ���ź���խ���ģ����������������źţ�ͨ�����������������ͼ 3b ��ʾ��ʹ��ʾ�����α꣬�����Եõ�����źŵ�Ƶ�ʷֱ�Ϊ 12.5MHz��25MHz �� 50MHz����ϸ����·�����֮�����ᷢ����Щ����ź������� 3 ��Ƶ���Ϲ����� 3 �������йء������ź�·��֮��û���㹻�ĸ��룬��Щ����ź���ʱ������ϡ�Ҫ���������⣬����Ҫ��ǿ�ź�֮��ĸ��롣

�ڶ���Ƶ���¶ˣ�����������һ�������ѹ۲�����ͻ���ļ���źţ���ͼ 3a �е���ɫԲȦ�У�����������ɷ������źš�����źŻ��Ƶ�źţ����翪�ص�Դ���Ƶ�ź�ͨ�ţ�����ġ���ʱ����ijЩʾ������ͨ���洢��������ޣ�������һ�����ڵĵ�Ƶ���������Ե�Ƶ����ֻ�Ǽ�Ъ�Եس��֡��˷���������һ��������ʹ��ʱ���е�ʱ��������Ƶ�ƽ��ֵ�����ַ������ͨ�˲���������ͬ��ͨ������������Ƶĸ�Ƶ������ֻ���µ�Ƶͼ�����ڣ����������ɵػ��Ƶ�Ƶ����ͼ��ʹ���α꣬���ܹ�ȷ��������Ƶ�ʡ�ͼ 3c ����ʾ��Ƶ�ʴ�Լ�� 180kHz������ܹ�ȷ������Ƶ��Ϊ 180kHz �Ŀ��ص�Դ�Ķ�������ϵ���ʱ���ź��С���ʱ��������Ҫ��ǿ�����Խ����ź���ϡ�

ͨ������ʱ�����������������Դ����ڲ����п���ȷ������Դ���������ⷴ������ƹ���ʦ��

ͼ 3a��ֱ��ͼ����ʾ��ʱ���������TIE����ʱ����Ϊʱ�����������Ƶ����Ϊ����Ƶ�ʡ�

ͼ 3b��ʹ���α���Բ���Ƶ���ϵļ���źš����Ƿֱ��� 12.5MHz��25MHz�� 50MHz����Щ�����ɷ�������е������йأ���Щ������ʱ�� PJ ����Ҫ��Դ��

ͼ 3c��ʹ��ʾ�����α��������Ƶ����Ϊ 180kHz��������ϵ�ʱ���źŵĿ��ص�Դ��ء�

�ܽ�

ȷ�����õ�ʱ�Ӷ������ܶ��ڱ�֤ DDR ϵͳ�Ļ�ͨ��������Ҫ��ʾ�����ϵ�һЩ���ù��ߺͷ����ܹ��������ڴ���ʱ�������ڿ���ִ��ʱ�Ӷ���һ���Բ���������Э�����Զ���Դ�ĸ���ԭ����з��������ǿ��Խ�ʡ���ı���ʱ�䣬�����������֤������

����Ķ�:

- ...2010/08/23 14:33��LabVIEW 2010�ķ����ͱ�������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������