���ֿ���DC��DC�任����ADC�����

DC��DC�任�������ֿ��Ʒ�ʽ��ģ����Ʒ�ʽ�����ֿ��Ʒ�ʽ����ͳ��DC��DC�任��һ�����ģ����Ʒ�ʽ�����������С�����ĵ͵��ŵ㣬����������Ӱ�졣�����ֿ��Ƶ�DC��DC�任���Թ��ղ����ͻ��������С������㷨��ͨ�����ʵ�֡����ڼ��ɣ����ܴ�����̲�Ʒ�Ŀ������ڡ������������ֿ��Ʒ�ʽ����Щ�ŵ㣬����DC��DC�任���õ����ǵĹ㷺��ע��

1 DC��DC�任���ṹ

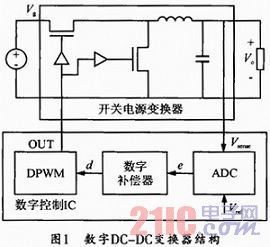

���ֿ�������Ҫ��ģ��ת����(ADC)�����ֲ�����(Digital Compensator)������������ȵ�����(DPWM)��ɡ�һ�ֳ��õ����ֿ�������ͼ1��ʾ������·�����ѹ�����ѹ��ADC���бȽϲ�ת��Ϊ��Ӧ����������źţ����ֲ���������������в����õ����������źš���DPWMת����ʱ���źţ���������·����ͨ�ϡ�

2 �ӳ���ADC

��CMOS������һ�������ӳ�td���Դ��ѹVDD߷������һ����ϵ

![]()

���У�K��һ�������������йصij�����Vth��MOS��������ֵ��ѹ����VDD����Vthʱ��td�ɿ�����VDD�ɷ��ȡ�

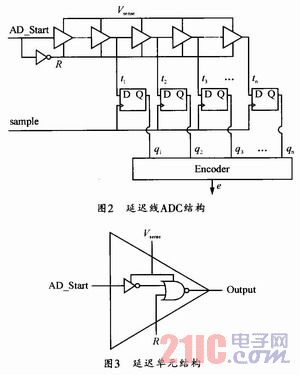

�ӳ���ADC���ӳ������Ĵ�����������·��ɣ��ṹ��ͼ2��ʾ��һ���ӳٵ�Ԫ����ӳ�����һ�ֿ��е��ӳٵ�Ԫ�Ľṹ��ͼ3��ʾ������һ����������һ������ż����õ���ÿ���ӳٵ�Ԫ����һ������ˣ�һ����λ�˺�һ������ˡ�

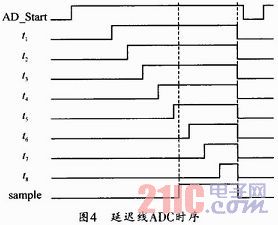

����һ����ʼ�ź�AD_Stan����һ��ʱ���������һ�����������ź�sample����ΪD�������Ŀ����źš��ڲ����ź���Чʱ��D�������������źŽ������棬��D������������ź����������·�õ��Ϻ������źš�ͼ4���ӳ���ADC��ʱ��ͼ������ͼ2��n=8���ڲ����ź���Чʱ��AD_Start�ź����ô�����5���ӳٵ�Ԫ������q1��q5���Ϊ1��q6��q8���Ϊ0��������ѹԽ���ӳ�ʱ��tdԽС���źŴ�����Խ�죬������¶ȼ����е�1�ĸ���Խ�ࡣ�����·�ٽ��¶ȼ���ת��Ϊ����Ҫ�Ķ������롣�ӳ���ADC��ͨ�������Դ���ӳ������磬�����ӳ����ӳ�ʱ��Ĵ�С��ȷ������Ĵ�С��

3 ����ӳ���ADC

3��1 ����ӳ���ADC�ṹ����

�ӳ���ADC�ṹ������С�������ܹ��պ��¶Ȼ���Ӱ�죬�Ҳ����ź����ⲿ�����������˵�·�ĸ����ԣ����Ҳ����źŵ��ӳٴ�С��Ӱ��ADC������ƽ�Ĵ�С��ʹ��ϵͳ��������ȶ���

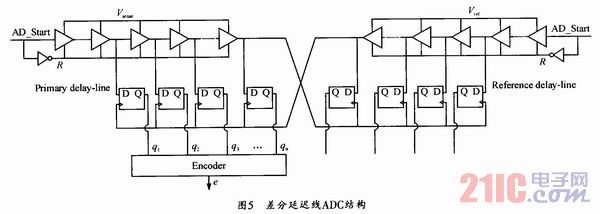

����ӳ��߽ṹ�Ƕ��ӳ��߽ṹ��һ�ָĽ����ṹͼ��ͼ5��ʾ������ӳ���ADC������ȫͬ���ӳ�����ɣ����ӳ���(Primary delay-line)�Ͳο��ӳ���(Reference delay-line)���ο��ӳ����ɾ����ӳ������ƶ�������������ӳ�������һ�������ź�AD_Start��ʹ�����ӳ����Ĺ���״̬��ȫ��ͬ������ӳ�������������ֱ��Dz�����ѹVsense�ͻ���

��ѹVref��Vsense��С��Vref�����ݵ�ѹԽ���ӳ�ԽС��ԭ�����ο��ӳ����������ӳ��������꣬�������ӳ���������D�������������ӳ����ϵ�Vsense���в�����������ʵ���˽�������ѹ�����ѹ���Ƚϣ���ͨ�������·�õ�ϵͳ��Ҫ����������źš�

����ӳ���ADC�Ŀ����ź����ڲ���������һ�����˵�·�ṹ�����ò����ʽ���룬ʹ�ò�����ѹ�ͻ���ѹͬʱ�ܵ��¶Ⱥ���ƫ���Ӱ�죬�������ӳ�������ʱƫ�

3��2 ����ӳ���ADC��ģ

���ӳ����е��ӳٵ�Ԫ����ΪN���ӳ�ʱ��td��VDD�ĺ�����td=td(VDD)������

��ת��ʱ��Tc�Ƿֱ���Vq���ӳ�ʱ��td�Լ��ӳٺ�����б�ʵĺ�����

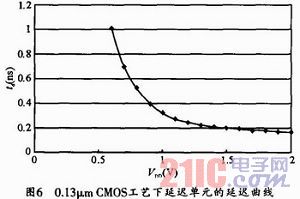

ͼ6Ϊ0��13μm CMOS�����µ����ӳٵ�Ԫ��VDD�Ĺ�ϵ���ߡ�

4 ��Ʒ����ͷ�����

�ӳٵ�Ԫ�Ծ���Ҫ��ϸߣ�����ȫ������ƣ��������·�Ծ���Ҫ��ϵͣ����û��ڱ��ⵥԪ��ƣ������·ʹ��Hsim������ģ��Ϸ��档

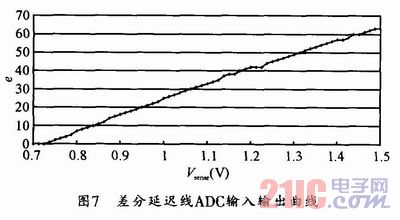

���ʱ������ѹΪ1��5V������Ƶ����1��5MHz�������ѹ��0��7��1��5V�������������Ϊ�����Ľ������6λ�����ź�e��Vsenseÿ���ӻ����12��5mV��e���ӻ����“1”����e�Ľϴ�ֵ��63��ͼ7Ϊ0��13μm CMOS�����²���ӳ���ADC������������ߣ����Կ���������ӳ���ADC�����û������ƫ�ƣ��������Ӧ����������Զ����á�

5 ������

�����ڷ�����Ӧ�������ֿ���DC��DC�任���е�ADC���ص�Ļ����ϣ��о��˲���ӳ���ADC�Ľ�ģ��ʵ�֡��ò���ӳ���ADC��·�ṹ������Ҫ�ⲿ��·���������źţ��ɵ������ֹ���ƫ���ADCת�����ʺܿ죬���ĵͣ��ʺ�Ӧ���ڸ�Ƶ����DC��DC�任���С�

����Ķ�:

- ...2009/07/14 10:23����������ң���Michelson�����Dz���̨��ʾ�������ֿ���

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������