����MIPS���̴߳������Ż�SoC���

�������߳���һ�ֻ���Ӳ���������Ĵ���������������ҪĿ���Ǽ������������ò�����������ܡ����߳�Ҳ��������������������Ա���Խ�����Ȩ���������ʱ�����е�����������������Ƶ��ؼ����ݡ������ϵĻ��������Ķ��̼߳������������л��ͻ����������̵߳����Ѿ��������൱һ��ʱ�䣬��������֪������Ӳ���Ķ��̵߳���ʷ������Ӳ���Ķ��̼߳�����ʵ�Ѿ��������൱��һ��ʱ�䣬��ʵ�ֿ����ݵ�20����60�����CDC6600����CDC6600�����У�10��Ӳ���̱߳�������֤��I/O��������Լ16����Χ�豸����Ӧʱ�䡣������ӵĴ����������ٶ�ԶԶ����������I/O�豸����һ��������ö��߳����Ƶĵ���Ӧ�ã���Ϊ���д���ʱ����Ա����̵߳��߳��л������湤����ȡ������70�����Denelcor HEP������CPU�ڣ���������I/Oʵ��ִ���߳��л����������������ս����ÿ�����ڵ�ָ�IPC�������������ơ�֮��10���Ƴ�����������ϵͳ��ѧ���о���һ��չʾ��Ӳ�����̵߳ĺô���

����������г�����������̴߳�������Ӣ�ض���˾�Ѿ������䳬�̼߳������ü�������߶˼���Ӧ�������⣬��������SoC�����̣���Broadcom��Lantiq��Mobileye��NetLogic Microsystems��PMC-Sierra��Ralink Technology��Sigma DesignsҲ�������ϰ�������ö��̴߳������IJ�Ʒ������������SoC�������˻���ҵ���MIPS�ܹ��Ķ��߳�MIPS32 34Kϵ���ں˻���̡߳��ദ��MIPS32 1004Kһ�´���ϵͳ��CPS����ĿǰӲ�����߳��Ѿ���Ϊ����Ӧ�ã���Խ��Խ����ΪSoC�����ʵ�ֽϼ����ܵ���Ч������

�����ö��߳������ˮ��������

������ǰ����������һ���������̴߳�������IPC������һ����ҪĿ�ꡣͨ������£���ʹ�Ƿdz������ܵĴ�����Ҳ�д���ʱ�����ã�Ŀ���ǵȴ����ݵ������������ǣ����й����洢ϵͳ�Ƚ��������軨50%��ʱ��ȴ������ڻ���δ�У�cache miss���ء������ݼ����ĵȴ�ʱ����ܻ������ʮ�����ڣ��ڼ�����������������ٸ����ڡ������������٣��������ڴ��ڼ����Ķ�����Ч���������̴߳����������ڶ���߳�֮���л���������Щ���õ����ڡ���Щ�������ڿ��������������̵߳�����ָ���������Ӷ�����δʹ�õ����ڰװ��˷ѡ�����ս���ø��õ���ˮ�������ʲ�����ϵͳ����������

����ȷ���߳��л�Ч�ʵ�һ���ؼ����������������߳������Ϣ���ᄈ�Ĺ�������ӳ�䵽һ���߳�ʱ��ÿ����������ص���������Ϣ�������������ͼĴ�����Ϣ�Ӽ�����Щ��Ϣ����Ӳ�����غ��µġ��ڵ��̴߳������У����ڴ��������߳�֮���л�����Щ�����ı��뵼�루swapped in�����������߳�֮��任ʱ����Ҫ���뱣��ͻָ������йصĶ���������ָ������ܻ��÷dz����أ������Dz��ø��ᄈ��high context���л������̴߳�����֧����ÿ��Ӳ��֧�ֵ��̵߳����������Ĵ洢�����豣��ͻָ����������ֻ���֧���л��̻߳������ĵ������ڿ�����

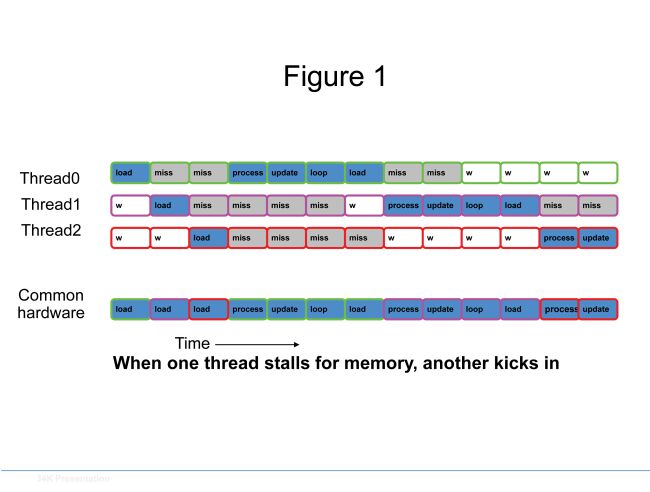

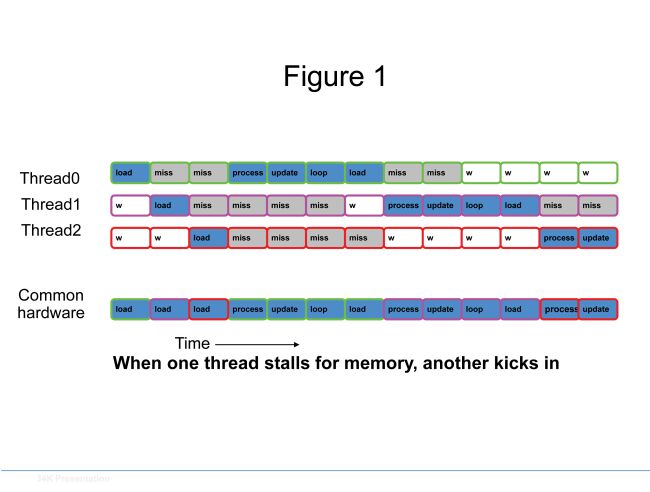

����ͼ1��ʾ�˶��߳�����������ˮ�������ʵĻ������ơ�����������£��ڲ�ͬ��ʱ����������̳߳����˻���δ�С�����Щ�߳���ͣ��stall���ڼ䣬�����߳���ͬһ����ˮ�����������õĹ������Ӷ�������IPC��

����

����MIPS���̼߳���

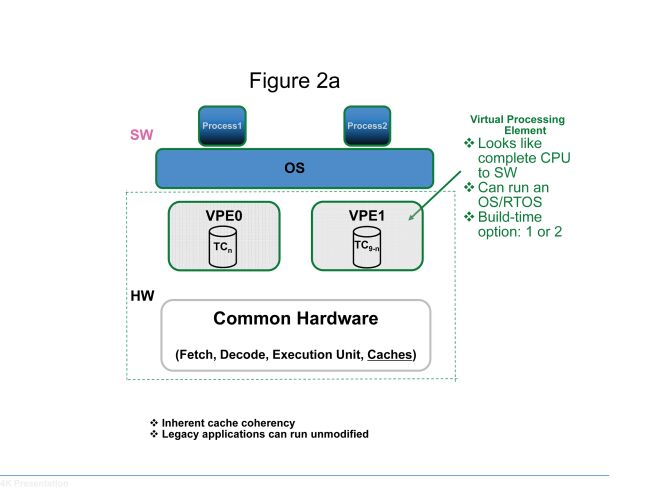

����MIPS�Ƽ��Ķ��̼߳�������������ο�ܣ��漰�������Ԫ��VPE�����߳������ģ�TC����֧��ÿ�����ڵ��߳��л���ÿ�����߳��ں˶���֧������VPE�����ǹ�������Ӳ����Դ�е�һ����ˮ�ߡ�����������ÿ��VPE�������Լ���Ը��ٻ����ת����������Translation Look-aside Buffer��TLB����������Ƕ�����Ϊ���һ��SMP Linux����ϵͳ�������������������֡����ڸ�ϸ���ȵ��̴߳���Ӧ�ã�ÿ��VPE����֧�ֶ��TC����ЩTC����һ��ִ�е�Ԫ�������и��ij�����������ں˼Ĵ����ļ����Ա�ÿ��TC�����Դ��������������̡߳�34K�ں˶�����֧�ַ���������VPE�ϵľŸ�TC��������ʱ�����Ż��ͷ��������ý�С��оƬ�����ִ��MIPS���̹߳��ܡ�

����34K�ں�Ҳ����Ϊ�̷߳��䴦�������ڣ�������һ����ѡ�ķ���������QoS����������������߳�����Ȩ����������ʵ���������Ȼ��ƣ�ȷ�������ϵ���Ϣ��������һ�����������û���ijһ���߳���������һ�����ڶ���������������ʱ��ı仯Ϊ�ض��̷߳���һ��ָ���������ʡ����������ƵĽ��ʹ�ÿ�����Ч�ظ��߳��������������õؿ����ӳ١���ʵʱϵͳ�У�ϵͳ���ľ����Ƿdz��ؼ��ģ���QoS�������ڸ���ϵͳ�Ŀ�Ԥ���ԡ�ͼ2a��ʾ��34K�ں���VPE��TC��QoS��Ĺ�ϵ��

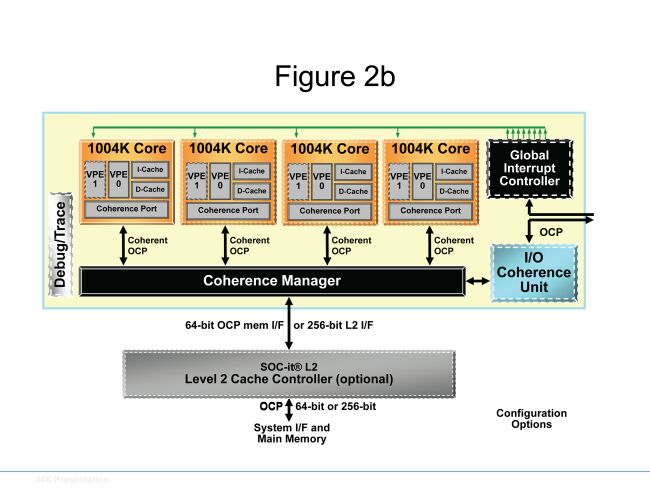

����1004K CPS��MIPS�Ƽ��Ľ���һ�����̴߳���������ϵͳ֧�ֶ���ĸ����߳��ںˣ�ÿ���ں˶���������Ϊ��34K�ں�����֧��2��VPE����1004K CPS�еĶ���ں�ͨ��һ��һ�¹�����Ԫ������һ���Ա���ÿ��CPU��L1���ٻ���֮���һ���ԡ�һ�¶��ں˼ܹ���ÿ���ں˵Ķ��̼߳�������1004K CPS����ͬ��̶߳�˴������������ܡ���ϵͳ������һ����ѡģ�飬Ϊ����I/O��Χ�豸�����ݴ����ṩһ���ԣ��Ӷ�ͨ��ж����Ϊ����ϵͳһ���֡�ͨ��������������I/Oһ���Է�����ö�������ܡ�һ�´���ϵͳ������һ��ȫ���жϿ����������Խ��ն��256���жϲ������Ƿ��䵽�ںˣ���ÿ���ں��ڵ�Ӳ���̡߳�����ϵͳ����MIPS L2���ٻ����������ͨ��һ����չ��256λ���ӿ����ӵ�һ�¹�����Ԫ�����Ż�һ��ϵͳ��L2���ٻ���֮�����������EJTAG��“һ�¹ܿ�”��������ݸ��ٿ�������ϵͳ��ͨ����������Ϊϵͳ�е�ÿ��CPU�ں˺�һ�µ�Ԫ�ṩ��ͬ�����ܼ��ȡ�

����SMP Linux����������VPE�ӿڵ�ЧӦ���Ӷ����ָ�API���䡣��ʹ�ö����д�ͳ�ں˵����������ں˳��ֺ�Ҳ����ı䡣���⣬һЩ����ThreadX��RTOS��SMP�汾������ϸ���ȡ�����TC�Ķ��̵߳�֧�֡�Ӧ��ָ�����ǣ�1004K�Ķ��̺߳Ͷ��Ӳ������������һ��ͨ�õ��������ģ�͡�Ҳ����˵�����磬������SMP Linux�������߳�Ӧ�ÿ�����Ч��������34K��1004K�ϣ��������ģ���SMP�ں˿���ʵ������������Լ����̺߳��ں˵Ĺ��������ؾ�����ߡ�����

����ͼ2a��34K����ܹ���

����

����ͼ2b��1004K����ܹ���

�������߳���һ�ֻ���Ӳ���������Ĵ���������������ҪĿ���Ǽ������������ò�����������ܡ����߳�Ҳ��������������������Ա���Խ�����Ȩ���������ʱ�����е�����������������Ƶ��ؼ����ݡ������ϵĻ��������Ķ��̼߳������������л��ͻ����������̵߳����Ѿ��������൱һ��ʱ�䣬��������֪������Ӳ���Ķ��̵߳���ʷ������Ӳ���Ķ��̼߳�����ʵ�Ѿ��������൱��һ��ʱ�䣬��ʵ�ֿ����ݵ�20����60�����CDC6600����CDC6600�����У�10��Ӳ���̱߳�������֤��I/O��������Լ16����Χ�豸����Ӧʱ�䡣������ӵĴ����������ٶ�ԶԶ����������I/O�豸����һ��������ö��߳����Ƶĵ���Ӧ�ã���Ϊ���д���ʱ����Ա����̵߳��߳��л������湤����ȡ������70�����Denelcor HEP������CPU�ڣ���������I/Oʵ��ִ���߳��л����������������ս����ÿ�����ڵ�ָ�IPC�������������ơ�֮��10���Ƴ�����������ϵͳ��ѧ���о���һ��չʾ��Ӳ�����̵߳ĺô���

����������г�����������̴߳�������Ӣ�ض���˾�Ѿ������䳬�̼߳������ü�������߶˼���Ӧ�������⣬��������SoC�����̣���Broadcom��Lantiq��Mobileye��NetLogic Microsystems��PMC-Sierra��Ralink Technology��Sigma DesignsҲ�������ϰ�������ö��̴߳������IJ�Ʒ������������SoC�������˻���ҵ���MIPS�ܹ��Ķ��߳�MIPS32 34Kϵ���ں˻���̡߳��ദ��MIPS32 1004Kһ�´���ϵͳ��CPS����ĿǰӲ�����߳��Ѿ���Ϊ����Ӧ�ã���Խ��Խ����ΪSoC�����ʵ�ֽϼ����ܵ���Ч������

�����ö��߳������ˮ��������

������ǰ����������һ���������̴߳�������IPC������һ����ҪĿ�ꡣͨ������£���ʹ�Ƿdz������ܵĴ�����Ҳ�д���ʱ�����ã�Ŀ���ǵȴ����ݵ������������ǣ����й����洢ϵͳ�Ƚ��������軨50%��ʱ��ȴ������ڻ���δ�У�cache miss���ء������ݼ����ĵȴ�ʱ����ܻ������ʮ�����ڣ��ڼ�����������������ٸ����ڡ������������٣��������ڴ��ڼ����Ķ�����Ч���������̴߳����������ڶ���߳�֮���л���������Щ���õ����ڡ���Щ�������ڿ��������������̵߳�����ָ���������Ӷ�����δʹ�õ����ڰװ��˷ѡ�����ս���ø��õ���ˮ�������ʲ�����ϵͳ����������

����ȷ���߳��л�Ч�ʵ�һ���ؼ����������������߳������Ϣ���ᄈ�Ĺ�������ӳ�䵽һ���߳�ʱ��ÿ����������ص���������Ϣ�������������ͼĴ�����Ϣ�Ӽ�����Щ��Ϣ����Ӳ�����غ��µġ��ڵ��̴߳������У����ڴ��������߳�֮���л�����Щ�����ı��뵼�루swapped in�����������߳�֮��任ʱ����Ҫ���뱣��ͻָ������йصĶ���������ָ������ܻ��÷dz����أ������Dz��ø��ᄈ��high context���л������̴߳�����֧����ÿ��Ӳ��֧�ֵ��̵߳����������Ĵ洢�����豣��ͻָ����������ֻ���֧���л��̻߳������ĵ������ڿ�����

����ͼ1��ʾ�˶��߳�����������ˮ�������ʵĻ������ơ�����������£��ڲ�ͬ��ʱ����������̳߳����˻���δ�С�����Щ�߳���ͣ��stall���ڼ䣬�����߳���ͬһ����ˮ�����������õĹ������Ӷ�������IPC��

����

����MIPS���߳�

����Ķ�:

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������