��δ����� di/dt ����˲̬���ϣ�

���ߣ�Robert Kollman���������� (TI)

�ؼ��ʣ���Դ��˫��������������Դ���С��ʿ����Դ������ģ�⡢�뵼�塢Robert Kollman������������TI

���������봦���� (CPU) ���ԣ��淶Ҫ���Դ�����ܹ��ṩ������ٵij������������ر��ǵ��������任����ģʽ��ʱ�����磬�� 1V ��ϵͳ�У�100 A/uS ����˲̬���ܻ�Ҫ��Դ��ѹ�ȶ��� 3% ���ڡ������һ����Ĺؼ�����Ҫ��ʶ�� �ⲻ�����ǵ�Դ�����⣬��Դ����ϵͳҲ��һ����Ҫ���أ�������һ���������������Ǻ��ѽ�������ϸ�ػ�����ޡ�

��Щ�� di/dt Ҫ�����������ڵ�ѹԴ������зdz��͵ĵ�С�������������Ĺ�ʽ�����õ������ĵ�Դ��У�

�ڿ��ٸ��ص���˲̬ͨ���е�н�Ϊ 0.3 nH��Ϊ�˱��ڱȽϣ���������һ���IJ��·���ϵ�0.1 Ӣ�� (0.25 cm) ����·���������еĵ�д�ԼΪ 0.7 nH/Ӣ�� (0.3 nH/cm)��IC ��װ�нӺ��ߵĵ��͵����1 nH ��Χ�ڣ�ӡˢ��·��Ĺ������0.2 nH ��Χ�ڡ�

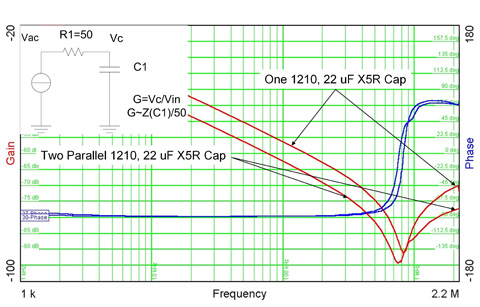

���⣬����һ������·�����йصĴ�����У���ͼ 1 ��ʾ����������������װ���IJ��·���ϵ�һ��22 uF��X5R��16V��1210 �մɵ��ݵ��迹������������������������100 kHz ���£����迹����Ƶ�ʵ����Ӷ��½���Ȼ������800 kHzʱ��һ��������У���ʱ���ݻ����е���ԡ��õ�У�����Դӵ���ֵ��г��Ƶ�ʼ���ó���Ϊ 1.7 nH������������� 0.3 nH ��Ŀ��ֵ�����˵��ǣ�������ʹ�ò��������Խ�����Ч�� ESL��ͼ 1 �ײ�������Ϊ�����������ݵ��迹����Ȥ����г����������һЩ���������Ч��в����Ǿ��Ե�һ�롣����г��Ƶ�ʣ������������ĵ��ݶ��ԣ��µ����Ϊ 1.0 nH ��ESL �½� 40%�������½� 50%����һ������Թ��Ϊ����ԭ������к���������֮��Ļ��С�

ͼ 1 ���������迹��������˥��Ч��

����ͨ���Ļ�·�ߴ���һ���̶��Ͼ�������������еļ�����У�����ߴ�����˻�·��������ߴ��������ϵ����� 1 ��ʾ������ʾ�˸��ֳߴ��մɱ�����װ���ݵĵ��ݵ�С�һ����˵�����Խ��ĵ��ݾ��и���ĵ�С��ñ���������·������װ���ݵĵ�У���������ǰ�IJ����иõ���� 1 nH ���ӵ��� 1.7 nH����һ����Ȥ�������Ƕ˽ӵ�λ�öԵ���кܴ��Ӱ�졣0805 �����ڵ��ݵĽ϶�һ���ж˽Ӷ�0508 �������ڽϳ���һ���ж˽ӡ��⼸��������ͨ����Ϊ�����룬�Ӷ����˵�С����ֱ仯�˵Ľṹ����н������ķ�֮һ��

�� 1 �մ� SMT ���ݳߴ��Ӱ��������

��֮���� di/dt ������Ҫ��ϸ������·�����Ա��ֵ�Դ��̬��ѹ��������װ������Ҫ�dz����������Խ�С���以����С����ݾ��п��ܱ������ȥ��ļ�����С�������һ������еIJ�����������Ч�ģ��������ͻ��м�������һЧ����ʹ�þ��и��̵���ͨ���ĵ���Ҳ����Ч�ġ�������������С�IJ�������н����˽ӣ���ʹ���˸��̵ijߴ����ڵ������IJ�����ʵʩ��

�´����ǽ����۸� di/dt˲̬�����Լ�������ƺͲ��Ե�Դʱ�����壬�����ڴ��� ��ʱ���ǵ������ص�ӱ�����·ת��Ϊ��Դ������塣

�����˽��йر����������������Դ��������ĸ������飬������ʣ� www.ti.com.cn/power��

����Ķ�:

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������