ADI ���� SHARC ��������Ƥ��

���ߣ�Paul Wheeler��GP-DSP ���ձ������ܼࡣ

ȫ�����ȵĸ������źŴ������������Ӧ�� Analog Devices, Inc. ���·��� SHARC ��������Ƥ�� -- SHARC ����������Դ���ݽ��������������£�

1. ����

˵��Ҫ�����ܵ�ǰ��Ӧ�ã��Ͳ��ò�����ADI��˾��SHARC�����������Ÿ��߶�̬��Χ���������ܺ��ͳɱ����г�ѹ�������վ���������Ӧ�öԸ��㴦����������Ҳ�ڲ������ӡ����Ľ����ܵ�һ��SHARC�������������ʷ����������ܹ��Ĵ��£���ʹ����������18��������źŴ�����ʷ��һֱ�������ȵĵ�λ��

2��SHARC ����������ʷ -- ��һ��

��SHARC���dz�������ܹ� (Super Harvard ARChitecture) ����д���� ADI ��˾Ϊ���ǵĸ��㴦����������֡�SHARC �������ڱ�����ܹ����������˸Ľ�������������PM (����洢��)�����ϵ����ݴ��ͣ���ͨ������һ��ָ����Ż��˻��ڽ���ѭ���ļ�����̵��������ܡ��Ľ���ļܹ��ܹ�ͬʱ��ȡ���ݺ�ϵ������ͬʱ��ָ���ִ����ѡ��ָ��Ӷ���Ч��ʵ���˴������������߲���ģʽ��

���֪����SHARC ������������Դ�� ADSP-21020��������㵥ָ����� (SISD) DSP ʵ������һ������Ƕ��ʽ�洢��������Ķ��������ںˡ�PM �� DM�����ݴ洢�����洢�ռ���ͨ�����ӵ� SRAM оƬ���ⲿ���߽��з��ʵģ�ͨ�� JTAG �ӿڶԴ��������б�̺͵��ԡ�

ADSP-21020 ������ 33MHz ʱ��Ƶ���¹�����ִ�е�����ָ�ADSP-21020 ��������80λ�ۼ������32λ��40λ�����32λ�������㣬�� ADI ��˾��1991�������г���ͻ���Բ�Ʒ�������ں˼����� ADI ��˾�Ը������ܺʹ���������ŵ����ʼ�㡣

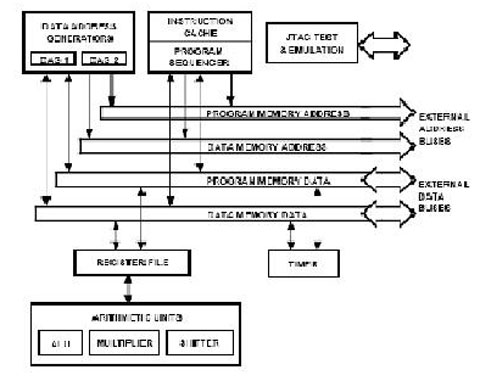

ADSP-21020�ܹ�

ADSP-21020����ϵͳ��ע������ PM �� DM �ռ���ⲿ DIP SRAM ��

�����봴�£�SHARC �ĵ���

��һ�������� SHARC �������� ADSP-21060��ADI��˾��ADSP-21020�ں˲�Ʒ�Ļ����Ͽ�������һ����ȫ���ɵĴ����������а��������ڿ��Ƽ�������� DMA ������Ƭ��SRAM��I/O��������

ADSP-21060 ���㴦������1994������г��ģ���ʱ����Ϊ��DSP���ܺʹ��·���Ķ���ˮƽ��

SHARC �ں��ܹ���һ���������Ըߴ� 40MHz ���ٶ�ִ�м��㣬���������� I/O ���������ܹ��ڲ������κ��ں˿����������£��������˫�˿� 4Mb SRAM �洢��֮����ٴ������ݡ�

Ϊ�˽�һ����߽����û���ϵͳ���ܺͿ���չ�ԣ�ADI ����Ŷ����ִ��������ദ����ϵͳ�ܹ������ݲ��ҿ�����С�Ļ��ơ����ⲿ�˿�����������һ�������߿�������������ؽ��д�������IJ�������ͨ�ţ�ÿ���ؽ϶������6��������������ͻ���Լ�������ϵͳ�ܹ�ʦ�Ըߴ� 240MBps �Ĵ���������������ָ���Ӵ��������ڴ�ֱ�Ӵ��ʹ������ݣ���ʹ�ù㲥ģʽ����е����д�����ֱ�ӷ������ݡ�

ʹ�� ADI ����·�˿�ר����������ʵ�ִ�������ĸ���ͨ�š�ÿ�� ADSP-21060 ������6����������·�˿����ڵ㵽��ͨ�ţ���˿���ʵ�ֶ���� 240MBps �� I/O ������

��һ�� SHARC ADSP-21062 ����ƽ̨

���ھ�����������ƽ��ļܹ�����չ���ܣ�SHARC ���������㷺��������ǿ�ȴ��Ӧ�ã���ҽ�Ƴ������״�͵�����Ϸ����

Ҳ�����˲������ţ��������ֹ��ܵĴ�������15��ǰ�������г��ˣ����������˸��Ӿ�����ǣ����ִ�����Ŀǰ���ڼ���Ϊ�û����ã����� SHARC �ܹ����ܵ�������չ���Լ� ADI ��˾���������û�����������ŵ�ĽϺ�֤����

�ڶ��� SHARC �������������������������µIJ�Σ������ں˼ܹ���չΪ��ָ�������(SIMD)ϵͳ�������ں�ʱ��Ƶ����ߵ� 100MHz��ADSP-2116x ϵ�д������������� ADSP-2106x SISD ��������Դ�������ȫ�����ԣ����Ҿ������������ľ������û����������ӵIJ������㵥Ԫ(�Ĵ����ļ� + �˷��� + ALU + Ͱʽ��λ��)�����ã�����һ�� SHARC ��ȿ��Խ���������ָ�����һ����

Ϊ���ڲ������������ܵ������·��㵽��������ӵ����㵥Ԫ�����ݴ��ͣ��ڲ��� PM �� DM �������߿��ȶ����ӵ���64λ��ͬʱ��ADSP-21161�ϼ�����48λ�� 100MHz SDRAM ������������ I/O ���ݴ��ʹ������Ӷ��ܹ�ʵ�ָߴ� 600MBps ���������ݴ���������

������һ�� SISD SHARC һ�����ڶ��� SHARC ������֧�ִ�����ϵͳ�ܹ��Ķദ�����������ӣ��Լ�ͨ����·�˿ڵĵ㵽�����ӣ�ʹ��������·��ͼ���Ӽ�������

������һ�� SISD SHARC һ�����ڶ��� SHARC ϵ��������ҽ�ơ���ҵ�;���Ӧ�����㷺���ã��������ڶ��⼯����֧��ʱ�ָ��� (TDM) �� I2S ��ʽ�Ĵ��ж˿� (SPORT)��רҵ����߶�����/���������豸�ܿ�����õ��˸ô������ĸ��������ṩ�Ĵ�̬��Χ���ơ�

������ SHARC ��������ʼ�����ദ����Ӧ�ÿռ䣬����ӭ���µ���ս����������ƵӦ���о������Եĸ��㴦�����ƣ�SHARC �����������ص㿪ʼת���Խϵ�ϵͳ�ɱ�Ŭ������Ƭ�ϴ������ܡ�

�����Ŀ�꿪���������г��ĵ�һ���������� ADSP-2126x ϵ�С����� ADSP-2116x һ����ADSP-2126x ���� SIMD �ܹ�ʹ�������ܽϴ����˽��ں����ܷ����ﵽ200MHz�⣬ADSP-21266���������� SHARC ϵ����������Ƭ����Ĥ ROM �IJ�Ʒ������ 4Mb ROM ������ϵͳ�����Ժͳɱ������������������¡��߳ɱ���ӡ��ĸ����� DSP ��������������Ƶ����

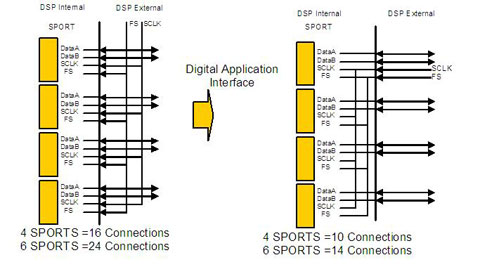

������ SHARC ������� DAI �������������������ͽ��ͳɱ�������

Ϊ�˽�һ������Ӳ��ϵͳ��Ƶĸ����ԣ�ADI ��˾����������Ϊ������Ӧ�ýӿڡ�(DAI)�Ĵ��������衣����ǰ�� SHARC ��ͬ�ྺ���Բ�Ʒ�����Ź��̶ܹ�������ͬ��DAI �����û����κ����蹦�ܷ��䵽������Ҫ������һ���ⲿ���š�������Ƶϵͳ��˵������ζ�ŵ�ϵͳ�������Ҫ�����ı�ʱ����Ƶʱ���������ʱͨ���������䵽���Ų�·�ɵ����ж˿ڡ���������Կ�����������Ϊ��֧������ϵͳ�淶������ⲿ����������������Ӳ����Ƶļ������û���һ�����ͳɱ���

ADSP-2136x �̳��� ADSP-2126x ��ʡ�ɱ����ŵ㣬���������Ƚ�����Ƶ�ź������ɷ������ں����������60%���ϣ��ﵽ 333MHz���ڲ� SRAM �����ӵ� 3Mb��������������������Ƶ�����裬��������첽������ת���� (ASRC)��SPDIF �շ����� DTCP �������棬�Ӷ���һ���Ż��˿ɱ�����ܺ���Ƶϵͳ BOM �ɱ��������� ADI ����Ƶ�г��е��쵼��λ������һϵ�еĸ����ܲ�Ʒ�л������˹���Ƶ�ʸߴ� 166MHz ��32λ SDRAM �ӿڣ������� I/O ������ͬʱ�����������ܼ�Ӧ��ʹ�����������Ĵ洢����

��������ͻ���Ե���Ƶϵͳ���ɺ��Լ۱��������ƣ������� SHARC ϵ�в�����רҵ��Ƶ��������������ƵӦ��(���ͥӰԺϵͳ��AV �Ŵ���)�еõ��˹㷺Ӧ�ã�Ϊ��һ��������Ƶ�� (DTS Master Audio��Dolby Tru-HD) �����г���������Ҫ���á�

���Ĵ� SHARC ϵ�� -- ADSP-2146x

���Ĵ� SHARC��ADSP-2146x �ܹ���ͼ

������SHARC ���������Ż��Լ۱ȷ���ȡ���˳ɹ����ƶ����㴦���������˶Գɱ����е�������Ӧ�ã�������Ӧ������������Ϊ�Dz�����ʹ�ð���ĸ��㴦�����ġ�

ADI ��˾����������һ������˼����ս����ν�һ���Ľ��߱������Լ۱ȵĸ��㴦������

�ڶ�����Ĵ�������ʱ����Ʒ�����Ŷ�ע�ص��Ǻ��ļ�ֵ����������ʹ�� SHARC һֱ���ڸ��� DSP ������ǰ�أ�

-- ���������

-- �ܹ�ƽ��

-- ���ܿ���չ��

-- ���ܼ���

���潫��ϸ��������ÿ���ؼ��ķ��档

ADSP-2146x ������ǿ

�� ADSP-2136x ϵ���ں˸Ľ��Ļ����ϣ�ADI �� SHARC �����Ŷ��ƶ��˸��ߵ�����Ŀ�꣬������̨���� (TSMC) �� 65nm �蹤�ռ����Ż����ܺͳɱ�ƽ�⡣ͨ����ϸ�Ĺ�����ƺ滮��ADI ��2008��11����ʽ������ADSP-2146x ϵ�д����������ں����ܿɴ� 450MHz����Ͻӽ��ľ�����Ʒ��ȼ����߳�30%��Ȼ����ADI ����ŶӲ��������ڽ�����ǿ���ܣ���ʼѰ���µķ�ʽ�����������������ܣ�ͬʱ�Թ��ĺͳɱ���Ӱ�콵����С��

�����ʦ���ø��㴦�����ṩ�Ŀ���̬��Χʵ�ָ����㷨����ͼ����⡢����ѹ��/��ѹ��������/���ܺ�����Ӧ�˲��������е����������ܼ����㷨�У����ٸ���Ҷ�任 (FFT)���������Ӧ (FIR) �˲��������弤��Ӧ (IIR) �˲�����һЩ�������źŴ�����Ԫ�õ��˹㷺ʹ�ã�����Ϊ����������źŴ���Ӧ�õĻ�����רע����Щ�ں��źŴ�������ģ��� ADI ��˾��ʼ����Щ���ܼ��ɽ� 2146x DMA �ܹ��У��Ա��

����Ķ�:

- ...2011/11/28 14:38��һ��ADI Blackfin����������

- ...2011/07/05 10:36��ADI����ģ��ǰ����ϵͳ ADAS1000 ����ϼ� ECG Ӧ�����

- ...2011/05/30 16:09��HD Radio? ��������������Ƶ����

- ...2009/09/27 14:46��ADI�Ƴ��ʺ�����VoIP�绰�ͺ������Ľ������

- ...2009/06/29 09:55���й��ǿز�ҵ�̺����̻���ADI DSP���ܱ�������

- ...2009/04/23 14:45��ADI�¿��ַŴ�����ҽѧ��������ͨ�ź������DZ���Ӧ��

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������