����ϵͳ����֮Դ

Silicon Labs 100��ʱ��IC��Ʒ��չ��ʱ��Ʒ��ϣ��Ÿ�����4-PLLʱ��ICӦ����������ս

������ģ�������ź�IC�쵼����Silicon Laboratories��о��ʵ��������˾������������ʱ��IC��Ʒ��Ͻ�����Ҫ��չ���������г��Ծ��гɱ�Ч��Ϳɱ�̼�ʱԪ������ǿ�����ù�˾���Ƴ���ҵ���Ÿ�����4-PLLʱ��IC����Ӧ�Թ�������ս����˾��ʱ��Ʒ�ܾ���Mike Petrowski��ý������˼�ʱԪ�������г��������Լ���˾�Ƴ��²�Ʒ���������ڡ�

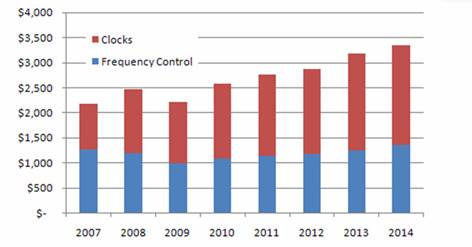

��ʱԪ�����г�DZ����

Mike Petrowski��ʾ����ʱԪ�����г���Ԥ��2011���г���ֵ�ɴ�25����Ԫ�������Ը�λ������������

ȫ���ʱԪ��������

��ʱԪ���������ڸ��������豸�����κ��п��ذ�ť���豸����ͳ�仯�������г��������ټ������ս��Ϊ�½�ҵ�ߴ����˻��ᡣ����ʱ�ӵ�PC CPU����ͳ��Ӧ�̵����������в���½�ҵ��������MEMS�������º���PLL�ܹ���OEM��Ӧ��������Ҫ���ǹ㷺��Ƶ�ʿ��Ƽ�ʱ�Ӳ�Ʒ��ͨ�������ն˶��Ʋ�Ʒ�������̽���ʱ�䣬���ٹ�Ӧ��ѹ����

�ڷ�����ʱ�г�����̬��ʱ��Mike Petrowskiָ������ʱ�г��ɻ���Ϊ�������г����м������г��ʹ����������г����ڶ�Ԫ���г������У�û���κι�Ӧ���ܹ����������г�����Ҳ����о��ʵ��������˾Ŭ��Ҫʵ�ֵĺ�ΰĿ�ꡣ��˾��Ϊ�ͻ��ṩ��һվʽ����ʱԪ�����ɹ������ǽϹ��������ʱ�Ӳ�Ʒ��ͨ���չ�SpectraLinear���ٽ�������������г������ô��µļ���ʹ��Ʒ���컯��ʹ��ר����MEMS��DSPLL��MultiSynth�����Ż����ܺͳɱ������ֶ��ƻ�ʱ�Ӻ�������Ʒ���쵼��λ�����⣬��Ҫ����Web����Ԫ�������ƣ����̽���ʱ�䡣��Щ�ٴ뽫�����ù�˾��2014��ǰ��Ϊǰ�����ļ�ʱԪ������Ӧ�̡�

�ٿ���Ʒ�����������г�

Mike Petrowski����˵��о��ʵ��������˾��������100���ʱ�ӷ�������ʱ�ӷ�������Ʒ��������Գɱ����С��д�����������������ѡ���ҵ��ͨ�ź�Ƕ��ʽ�����Ӧ����������ʱ�Ӳ�Ʒ��ϵ���չ�������ڽϽ���SpectraLinear��˾���չ�����һ��ȷ����Silicon Labs��˾��Ϊҵ���ȫ��ļ�ʱIC��Ӧ�̵ĵ�λ�����ṩ���Ƿ�Χ�Ϲ㷺�Ļ���źŵͶ���ʱ�ӡ��������������Ȳ�Ʒ��

�ݽ��ܣ�Silicon Labs�����ӵ�ʱ�ӷ������ͻ�������Ʒ�����нϵ��ġ���С�ߴ�ͽϺõ�Ƶ������ԣ���Ҫ���400MHz���¶Գɱ����е�Ӧ������ϵ�е�ʱ�ӷ�����������ͬ��ʱ�Ӳ�Ʒ��20-40%�Ĺ��ģ��ϴ��ȵ���չ�˱�ЯʽӦ���еĵ��������ͬʱ��ϵ��ʱ�ӷ������ķ�װ�ߴ�Ҳ�Ⱦ������ֵIJ�ƷС30%���������˫�����װ�Ľ�С�ߴ��1.8mm �� 2mm����Щ��С��ʱ�ӷ�������Ϊ�ռ����ı�Яʽ��������Ӧ�õ�����ѡ��

���õ�1��4·PLLʱ�ӷ������ܹ�����ǰ��δ�е�����ԣ�������ƥ�����Ӧ�öԳɱ������ܵ���������ʱ�Ӽܹ���ͨ�����������Ż��������ܡ����ܺ�ϵͳ�ɱ���Silicon Labs��˾Ϊ�ͻ��ṩ�ѺõIJ�Ʒ���úͶ���������Ӧ��ƺ��ڶ�ʱ�Ӳ����ı仯���Ӷ��ܹ��ṩ֮ǰ�����������ṩ�Ĵ��������Ƽ�ʱIC���������

����ʱ�ӷ������ṩ������/�½�ʱ�䡢����迹��չƵ��Χ�����ƫб��Ƶ�ʷ�Χ����������Ϊ����������2�����ϣ�ʵ����ͬ���Ʒ�ϼѵĵ�Ÿ��ţ�EMI�����Ƽ�������Щ�����ɶ��Ƶ��źŲ���������EMI���⣬���������̲�Ʒ����ʱ�䡣

Mike Petrowski��ʾ���������ڵ��ġ�С�ߴ�ʱ�Ӻͻ�������Ʒ�ߵ����䣬������չ��Silicon Labs��Ծ��гɱ�Ч��ʹ���������Ӧ�õ�ʱ��IC��Ʒ��ϡ���Ϊʱ�Ӳ�Ʒ�г������ȵļ��������ߺ�����һվʽ�ɹ�����Ҫ����źż�ʱ���������Ӧ�̣������ṩƵ�����ɶ��ƵĵͶ���ʱ�Ӻ�������Ʒ����������ּ۸�Χ����������Ϳ������ڡ���

4-PLLʱ��ICӦ�Թ�������ս

�ո��Ƴ���ҵ���Žϼ����ܡ��ϸ��ɶȵ�ʱ��IC����Ӧ�Ծ߱�����ʱ��Ҫ��ĸ��ٹ�����磨OTN��Ӧ�á����øù�˾ר����DSPLL®���������Ƴ���Si5374��Si5375��ҵ���һ������ĸ����������������·��PLL���ĵ�оƬʱ��IC�������ṩ��PLL��������������������������������������40%��

OTN����һ��Э�飨ITU G.8251��G.709�����Ը���Ч�ʵķ�ʽ�ڹ��������ṩ�������ķ���Ϊ��Ե·���������ָ��ã�WDM������װ�á����ż���̫���Ͷ��ط���ƽ̨��������������OTNӦ�������˸��ӵ�ʱ����ս����Ϊ����Ҫ�����������أ�non-integer-related��Ƶ�ʵĵͶ���ʱ�ӡ�Silicon Labs Si537xԪ����������DSPLL���ɲ������˸��Ͷ������ʱ�ӣ����κ�Э�顢����˿ڵ�10G��40G��100G OTN�߿���ơ�

DSPLLʱ�ӱ�Ƶ���ɷֱ����ã����ɴ�2 kHz �� 710 MHz�����������2 kHz �� 808 MHz������Ƶ�ʡ����������Ƶ�ʵ��Կɽ��Ͷ�Э��OTN��·���ijɱ��븴�Ӷȣ���Ϊ���Ѷ��ض�������ʱ��IC�������ϵ͡�Si537xԪ�����߱�ҵ�����ȵ�0.4ps�������ܣ��䵯��DSPLL�ܹ��ɼ���PHY�ο�ʱ�ӡ���ˣ�OTU3��OTU4��Ӧ�ñ�����ʹ�÷���ʽ����VCXO��PLL��

Si537xԪ��������Ҫ�ָ����еʹ���PLL�����ɾ������������ʱ�����룬����Ҳ��OTN��·����ʱ�ӵ���ҪҪ�������ĵ��ż����ܻ���������SONET���ݵĶ�����ֵ���ϴ�Ϊ0.1 dB�������µ����ж��л��������ܽ��ο��л�ʱ�����ʱ����λ˲�併���ϵͣ�������������λ˲������������������С25����ÿ��DSPLL���涼�߱���ȫ���ɵĻ�·�˲�������֧�ֵ���4 Hz��ʹ���߱�̴���������һ�����Ư�ƹ��˺Ͷ���˥�����������ÿ�����������á�

Mike Petrowski��ʾ����OTN�ϸߴ������ݡ�Ӱ������������Լ���ѧ�߿��Ӷ˿��ܶ����վ��������ⶼ��Ҫ���߶ȵ�ʱ�Ӽ����볬�͵Ķ��������ܰ���Ƴɱ��븴�ӶȽ����ϵ͡�Silicon Labs���Ƴ���Si537xʱ��IC��ҵ��ϵͶ�����������������������ṩ��ǿ��ĸ�����PLL����������Ϊ��ǰרΪOTN����Ƶ�ʱ�ӽ�������������±�͡���

Si5374Ԫ�����а˸�����ʱ�ӺͰ˸����ʱ�ӣ�Si5375��Ϊ��Ҫ����ʱ�ӵ�Ӧ���ṩ���ĸ�����ʱ�Ӻ��ĸ����ʱ�ӡ�ƾ��������DSPLL����̬��һ��Si5374ʱ�ӿ���ͬʱ������ͬ��Ƶ�ʣ���ʵ�ּ������һ������ƣ����ͬʱ֧��SONET/SDH��1/10/100G��̫����1/2/4/8/10G��������3G/HD SDI��Ƶ���Լ�������Э�顣

Si537xʱ���ṩ�˱���������������ʹ�ͻ����Դ�Silicon Labs��Si5319/26����˥��ʱ�ӣ�ת�������ɶȸ��ߵĶ�������ʱ�ӽ�������������������嵥�ɱ��븴���Խ����ϵ͡��ڸ߶˿���10G/40G/100G OTN�߿�Ӧ���ϣ�Si537xʱ��Ԫ��������Ч�Ե�һԪ����ȡ���ĸ�ʱ��Ԫ������

����Ķ�:

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����