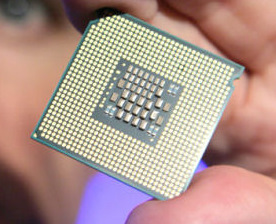

�й�32nm�����Ų�����

32nm�����ǻ��ж�Զ�������ѵ�����ͻ�ƣ��������豸Ҫ���ݺ��ֽ�ɫ��10��28���ڱ����ٰ���Ƚ��뵼�弼�����ֻἴΧ�ơ�32nm������չ����ս����һ���������̽�֡�

32nm�ڵ���ս����

��45nm�ѽ���������32nm������С��22nm�����ٵ���ս�Ѱ���������ǰ������о���������з����ܲü�������ʿ�������ݽ�ʱ˵����������˵�����ĸ�����ֵ������ע�⡣������CMOS�����������洢���������ļ�����һ�������SOC�����ľ���ս�����������ȣ����������ڱȽ����ŵ�3D IC��SIP���ɣ��Ϻ�һ������ν������㷺���з�ƽ̨�����ϻ��ƣ�������ν��super foundry����32nm�������پ���з��ɱ���������ս����Ҫ��ϸ�����Դͨ������������ȫ���ݵ�CMOS����ƽ̨��ȫ����IP�Լ�ȫ����ȫ����оƬ����������δ���ķ�չ���ơ�

KLA-Tencor�й��������ܼ��ν��ʿ��Ϊ������оƬ������˵�����տ���������Ҫ��45nm�ڵ�IJ��������ѳ���200��������32nm���С�ڵ㣬���վ���Ҫ���Ϊ���̣������������ӷ����������ܹ�Ԥ֪�����Ѽ����ڸ�k����դ���ֵ�channel���տ��ơ���Ĥ��ȱ�ݵļ�⡢��Ƭ����ȱ�ݵļ�ʱʶ���жϵȡ���С�ڵ���ζ��ͼ�θ���ϸ���µ�ȱ��Ҳ�����������������Ⱥͷֱ��ʱز����١����ν��ʿ̹�ԣ���ͬʱ������ҵ��ͬ�ڵ����з�����������Ч���и��ߵ�Ҫ����������ٶ�Ҳ�����Dz��ɻرܵ����⡣��

��̹��������ͷ������

��̼��������ǰ뵼�弼����չ·��ͼ�е���ͷϷ�������������ۺ��о������ڶ���ASML���й�������ս���г�����Curtis Liang��ʿ��32nm�ڵ��̼����Ľ�չ�����˲�������32nm���ڴ洢������������˵��һ���µ�ת�۵㣬��Ϊ�ܶ��µļ����������ﱻ���á���Curtis Liang˵������С�ڵ��������ʽ����Ѻ���������������̽�������Һ�����������в�С�Ľ����ռ䡣���ڴ��Ҳ����̸��˫��ͼ�Σ����Ǵӳ�Զ�Ƕ���������Ӧ���ǽ���ʽ�����EUV���֮���һ�����ɡ���

Cymer�����������Ӧ���ܼ���˼����ʿ��Ϊ��32nm�ڵ���ڹ�̹�����˵����ζ�����ʵ�־�ȷ��դ��CD���ƣ�������Ե�ֲڶ��Լ�OPC��Ҳ���������ء���Դ�ǹ�̻��Ͻ���Ҫ����ɲ���֮һ����Դ���������ȶ��ԡ���������ij�̶ֳ���Ӱ���Ź�̼����ķ�չ���ر���δ���п��ܻ���õ�EUV��̣���Դ���������Ǿ������صġ�32nm�ڵ�Ŀǰ���������Խ���ʽ������˫��ͼ�μ���Ϊ���������·�չ��EUV�Ļ��Ὣ��ܴ�

�뵼����ϲ��ݺ���

��Խ��Խ����²��ϱ�����뵼������ʱ�������������������������ǵ���Ȥ��Cabot�������з��ܼ��������ʿ��32nm�ڵ��CMP����������Լ��Ŀ�������CMP���������������кܴ�IJ�ͬ���Ǿ����������������ڲ��ϣ�����ĥ�Ϻ���ĥ�棬�����仰˵�����ϵķ�չ������CMP�����Ľ��������������ʿ˵�����������ڳ����ᵽ�ĺܶ��½ṹ�����k����դ�͵�k�����ȶ������˺ܶ����˲��ϣ�CMP����Ҫ��Ѹ�ٵ�ʵ�����Ŀ�ģ���Ҫ��֤�������ٵIJ�����ȱ�ݡ�Ŀǰ���з��ص��Ƕ��ڲ�ͬ����ʵ�����õ�ѡ��ȣ����ٻ��˵�ȱ�����⡣

�������ӵ���������ʿ��ǿ���˻�������Ҫ�ԡ�CMP���ϵķ�չ�����в���Ҫ���Ǽ����;������أ����ڲ����������Ļ�������Ҳͬ��ֵ��ҵ����˼��

����Ķ�:

- ...2009/05/18 09:36���й�3G������������ �۸�ս֮������DZ��

- ...2009/04/29 09:18���ձ���������̫�ɷû� ���й�3G�г�

- ...2009/04/13 09:46��LG����������ȫ������й�3G����

- ...2009/03/25 10:05���������й�3G ����˶Զ˽������

- ...2009/03/03 19:22��TriQuint�����й�3G����

- ...2008/11/13 09:40����˼�������й�3G�г�

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����