���Ⲣ���������������ϵͳ��������� - �ڶ�����

���ߣ�Kedar Godbole���������� C2000 Ӧ�ò�Ʒ��

�ڱ��ĵĵ�һ�����У�����̽���˲������̼��㷨ʵʩ������ЧӦ�������������ʵ������ӡ֤��һ���ֵķ��֡�

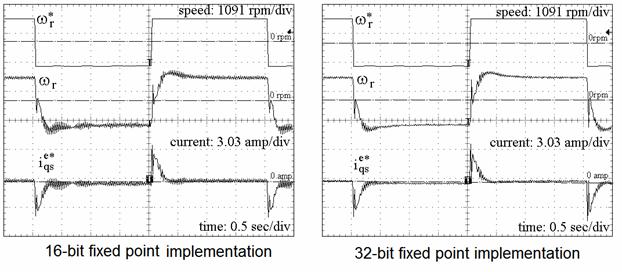

��ͼ 1 Ϊϵͳʵʩ�ṹͼ����ǰ�������ڱ��ĵ�һ�����У����Dz��� 16 λ���㼰 32 λ���� DSP ����ϵͳʵʩ��

ͼ 1. �������ϵͳ��ʵʩ

Ȼ�������ڶ��㴦�����ϵĸ���������ͨ������ʱ��֧�ֿ� (rts2800_ml.lib) ʵ�ֵģ�����Ч�ʲ��ߣ����Ը���汾����ʵʵʩ��ʽ��Ҫ�ϳ��IJ���ʱ�� (4 kHz) �Ա�������и���ģ�顣���ڲ�ͬ�IJ���ʱ�佫Ӱ��ϵͳ���ܣ�����Ϊ�˱ȽϷ��㣬ʵ�������������� 16 λ�� 32 λ֮��Ķ���汾���ڲ���ʱ�䲻�����������£������� 32 λ����汾����Ӧ����ͬ�ģ����һ������������

�������ֿ������Ļ��������Dz��� 32 λ�ֳ������� 16 λ����汾�����������ľ��飬���� 16 λ�����ۼӵĽ�����Եز�Ķࡣ�������Ʒ���IJ��Խ� ��0.5 pu �IJ���Ӧ����ϵͳ�ٶȲο���d �ἰ q ����������ٶ���Ϊ�ٶ�����IJ�������ЩҲ֤ʵ�˷���������˲̬����̬״̬�£�����������Ӧ����Ժ�ǿ��������˲̬������� 16 λʵʩ��ɵ�˲̬ʱ�����ӵ�����µ�����ЧӦ�ǿ�����֤�ġ�

ͼ 2. ʵʩ�Ĺ����ٶȼ� q �����

����������Ƶ��

Ҫ�������źŴ���������������㷨��ʵ�� PID �ȿ��������ÿ�������������ɢ������������Ƶ�ʵ�ѡ���ǹؼ��Ŀ������أ�������ѭ�ܹ�����ʧ������˹�� (Nyquist) �涨��Ȼ���ڿ���ϵͳ�У��������ʼ��������б�Ҫ�����˹�ع涨����Ĵ�Ķࡣ������ϵͳ (![]() ) �ϸ�Ƶ�ʷ���ʱȷ������Ƶ�ʡ�Ȼ����ѡ�IJ���Ƶ�� (

) �ϸ�Ƶ�ʷ���ʱȷ������Ƶ�ʡ�Ȼ����ѡ�IJ���Ƶ�� (![]() ) ������ڸ�Ƶ�ʵ���������

) ������ڸ�Ƶ�ʵ��������� ![]() ������ѭ���˹�ع涨������ȷ������ϵͳ������������ˣ�����һ��ϵͳ (first order system) ���ԣ�ͨ����������ѡ��Ƶ�ʴ���

������ѭ���˹�ع涨������ȷ������ϵͳ������������ˣ�����һ��ϵͳ (first order system) ���ԣ�ͨ����������ѡ��Ƶ�ʴ��� ![]() ���ı����ϡ����ڶ������ϵĸ��߽�ϵͳ���ԣ�ͨ��ѡ�������Ϊ�ϸ�Ƶ�ʷ����� 10 ����

���ı����ϡ����ڶ������ϵĸ��߽�ϵͳ���ԣ�ͨ��ѡ�������Ϊ�ϸ�Ƶ�ʷ����� 10 ����

��������Ŀ����Ϊ�˽��ڲ�����ƫ�� (inter sample deviation) �����ڿ��Խ��ܵĽ�С��Χ�ڡ�Ϊ˵������������� 1 �г��˲����ʱ仯ʱ�Կ�����ϵ����Ӱ�졣�ڴ����У����ǽ�һ���ĵ����㴫�亯����������ɢ������(1) Ϊ���亯���Ĺ�ϵʽ��

![]()

ʹ������������ Matlab �н�����ɢ������

MATLAB>>SYSD= c2d(tf([100],[1 100]),Ts,��zoh��)

���ǿ��Կ��������������ѡ��ǡ������ϵ������������Ե����⡣�������������������ķֱ������⡣ͨ���۲��ϵ���ķ��ȿ����˽�����ЧӦ��������ϵ���ֱ������⡣���Ų����ʵ���ߣ�����ϵ�� (numerator coefficient) ��С����������Ϊ ![]() ʱ��ϵ���½�Ϊ 0.00099950016���� Q15 ��ʾΪ 0x0020���� 16 λ�������ı����ϼѵ����ȷֱ��� (single precision resolution)������ζ��ϵ���ֱ���Ϊ 5 λ������ϵͳͨ�����漰�졢����̬���Ի�ϲ���Ҫ���ӵĴ������̣����Զ�16 λ��������˵�Ǹ������ص����⡣

ʱ��ϵ���½�Ϊ 0.00099950016���� Q15 ��ʾΪ 0x0020���� 16 λ�������ı����ϼѵ����ȷֱ��� (single precision resolution)������ζ��ϵ���ֱ���Ϊ 5 λ������ϵͳͨ�����漰�졢����̬���Ի�ϲ���Ҫ���ӵĴ������̣����Զ�16 λ��������˵�Ǹ������ص����⡣

������ֱ��������ܵ���ʵ�ʿ������ᷢ����λ�ơ�����ֳ������ģ�Ͳ�ͬ�����ԡ���Щ������ܵ������ص��������⡣���� 16 λ���������ԣ�Ҫ���ָ�Ч�ʾͱ���߱� 16 λϵ�����������������ڹ����ܼ����������ʦ��ϵ��ѡ��Χ�Է��Ӷ��Խ��� 4��5 λ�ķֱ��ʡ���ЩӰ�춼����Ϊ��߲���������ġ����ϵͳ���ʦҪ���ϵͳ��������ôҲ������߲����ʡ�����������£����� 32 λ�����ʹ��ֵ��ʾ�õöࡣ�����������ʱ����TI TMS320F2812 �����źſ������Ⱦ��б��� 32 λС����ʾ������ 32 λ���������Ա�������������⡣

���� PWM �ܹ����併Ƶ�������������

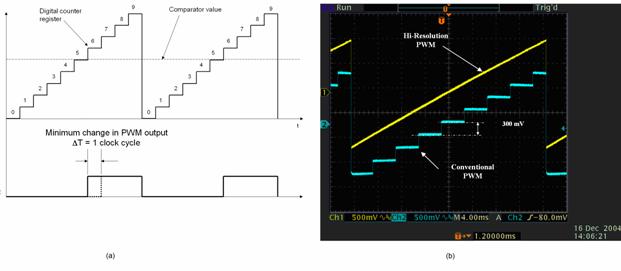

Ƕ��ʽ�������������������� (PWM) �ܹ��������ּ�������ȽϼĴ��������� PWM ���������ʱ��Ϊ�������ṩʱ�ӣ����������������ֵ��ȽϼĴ�����ֵ���Աȡ���������ֵ�����ȽϼĴ�����ֵʱ��PWM ���ű���Ϊ�ߵ�ƽ��ͨ�����ıȽϼĴ�����ֵ�Ϳ��Ե��������ͼ 3(a) Ϊ�����ʾ����

���ַ���Ҳ����ȱ�㡣PWM ����Ľ�С�仯ֵ���ڼ�����ʱ�ӵ�ʱ�����ڣ��� PWM Ƶ������ʱ������������⡣���磬��ʱ��Ƶ��Ϊ 50MHz��PWM Ƶ��Ϊ 25 kHz ʱ��PWM �ֱ���С�� 11 λ���������ڸ߾���Ӧ�á�ռ�ձȱ�Сʱ���Ƚ��� 2 �� 3 λ�������� 300V DC �������� 24V �� 36V �ŷ�����������ͬ�������ƹ�������У������������Ʒ����������ʱ����������Ե��淢��Ҫ�������У�PWM Ƶ��һ����� 200kHZ����Ҫ��Ϊ�˽��ʹ��������Ĵ�С�������е� PWM Ƶ�ʼ�ʹ�ﵽ 100MHz����ֱ���Ҳ��Ϊ 8 �� 9 λ������ܵ��������������⣬Ҫ��������⣬�������� PWM �ܹ���

TI ����Ϊ�߷ֱ��� PWM �����ͼܹ����״�Ӧ���� TI TMS320F2801��F2806 �� F2808 �����źſ�����������ȫ�µĵ��Ʒ������ֱ���Ϊ 150 �롣������ת�������Ӧ�� PWM �ֱ���Ҫ�ߵĶ࣬������������������������������Ӱ�졣

ͼ 3. �� PWM ����ͼ���Լ��߷ֱ��� PWM �봫ͳ PWM ��ʾ����ͼ�Ƚ�

ͼ 3(b) ��ʾ�������еĸ߷ֱ��� PWM ���� PWM �������ο�����ͼ�ε�б�棬�����ø߷ֱ��ʹ���ʱ����������������ø߷ֱ��ʹ���ʱ����Ļ����ʾ�˻�ɫ�������������߷ֱ��� PWM �����˼����������� PWM ������������ڷ������� PWM �����������ԣ����� PWM ��ʱ��ֱ��ʼ�ת��Ϊ�����ѹ�ֱ��ʣ��߷ֱ��� PWM ��������ǿ�ֱ��������ڽ�������������ֱ��ʶ����µ�������������ķ�����

����

��������ʵ�����ıȽ���ʾ��16 λϵͳ�����ܸ����ܴ���һ���棬32 λ����ϵͳ�������븡��ϵͳ��ͬ����Ϊ����ĸ����Դ�Ϊ��ή��ϵͳ���ܣ�����ڶ���������ʵ�ָ����㷨�Dz���ʵ�ġ�Ȼ����ƾ���оƬ�����Ľ����Լ���С�ɵİ뵼��ߴ磬�������ڽ����Ƴ��˳��ͳɱ��� 32 λ���������źŴ��������Ӷ�ϵͳ�����Ա�ܹ����� 32 λ��������������ϵͳ�����ܡ�

���⣬ѡ�� 32 λ���㷽������ʹ�����Ա�ܹ��Ӽ������ϸ������ȷ����Ĺ����н��ѳ��������һ���ʹ�ø��ߵIJ����ʣ��Ӷ���������˶��ŷ������Ա��˵������Ҫ��ϵͳ������Ϊ�˶�����ЧӦ��һ�����������⣬��ʹϵͳ���ܽ��Ż�����������������Ҳ����Ҫ�������߷ֱ��� PWM �ȼ��������ƣ�

����Ķ�:

- ...2011/05/27 09:57�����Ⲣ���������������ϵͳ��������� - ��һ����

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������