����XC2C64AоƬ������¼���ʳ��źż���·���[ͼ]

��¼�������У����ϵͳ�ǽ���Ҫ�IJ��֣��뿪�����ϵͳ�еľ�������дֲ�������ʧȥ����[1]���������ϵͳ�У��߶ȵIJ����ǽ�Ϊ�ؼ��ġ�ͨ���ʳ��źŵ�ʵʱ���ݼ�⣬�ɵõ���߶���صĽʳ������źż���ֵ������ֵ������λ����ͨ����Ӧ�ļ�����Եõ�ʵʱ�ľ��

ͬʱ������̫���ܺ����ع��������¼�����ݲɼ��봫��ϵͳҪ���ֳ��ʳ��źż���·������е��ġ�С�ߴ�Ϳ�������ǿ���ص㡣��ˣ����÷���Ԫ��������ƵĴ�ͳ�Ľʳ��źŲ�����·�Ͳ�����������¼��ϵͳ����Щ����Ҫ��

����Xilinx��˾��CoolRunner IIϵ��CPLDоƬXC2C64A���XC9500ϵ�еĸ��ٶȡ��������ú�XPLA3ϵ�еij����ĵ��ŵ㣬���е��ġ����ܶȡ���ϵͳ�ɱ�̺Ϳ���������ǿ���ص�[2]����һ��оƬ�ϾͿ��Դ����Ŵ�ͳ��оƬ��ʵ�ָ��ӵ������ʱ�������ƣ��ܹ��ﵽ���ġ�С�ߴ�Ϳ�������ǿ����������[3]��

����¼���ʳ��źż���·�������ʵ��

�ʳ�˳ʱ����תʱ�� ���������A�ನ�γ�ǰB�ನ��90°����ʱ����תʱ�����A�ನ���ͺ�B�ನ��90°�����ļ���(�������)����Ƶ�ͼ������ǻ���������������������źš�

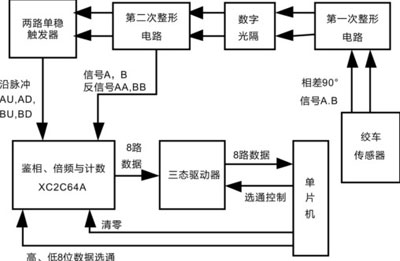

�ʳ��źż���·������ṹ(ͼ1)�������ʳ��źŵ����Ρ����롢���ࡢ��Ƶ�����������ݶ�ȡ�ӿڵȲ��֡�

�ź�A���ź�B�����Խʳ�����������λ��90?����·�����źţ��Ⱦ�����һ��ʩ�������Σ������ֳ����ź���·˥����������岨�λ��䣬ת��Ϊ���������źţ�Ȼ�����ָ��������е������룬�����·һ����Ժ���ĵ�·�𱣻����ã���һ�������ѹ�任�����ã����ź�ת��Ϊ3.3V����ѹ�������źţ��پ����ڶ���ʩ�������ε�·�������Σ��˴����ε���ҪĿ���ǽ���·�����źŵIJ��ν��б任������A��B��AA(A�ķ���)��BB(B�ķ���)��·�źš�

ͼ1 �ʳ��źż���·�ṹ��ͼ

���ڶ������κ�A��B��·�źž�������̬�����������������غ��½��ش��ֱ���д������õ��ĸ�խ�����ź�AU��AD��BU��BD��

�õ���A��B��AA��BB��AU��AD��BU��BD��8·�ź����뵽CPLD XC2C64A�����б�Ƶ������ͼ����ȴ��������ڵ�Ƭ���Ŀ����¶����ݽ�����������㡣

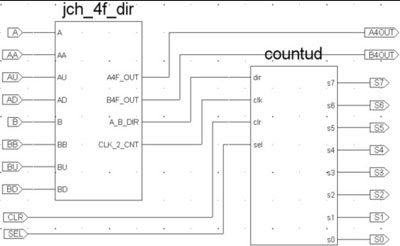

�������ϵ����ԭ��������Xilinx��˾��EDA����ISE��ģ�黯���[4]�ķ������������¼���ʳ��źŵļ���·���䶥����Ƶ�·��ͼ2��ʾ���õ�·����������ģ�飺��Ƶ��������ģ��jch_4f_dir������4��Ƶ�ͷ�������ܣ�16λ�����ƿɿؼӼ����������ݽӿ���ģ��countud�����м�/������(�ɷ�������źſ���)��MCUѡ���ȡ��/��8λ�������ݵȹ��ܡ��õ�·��XC2C64A-7VC44I����[5]�Ͻ��������ز��ԡ�

ͼ2 �ʳ��ź��ı�Ƶ����������������·ͼ

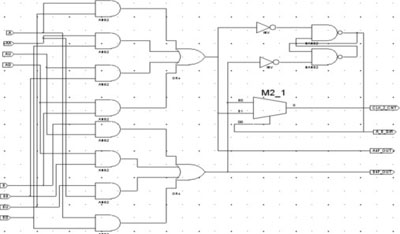

A��B��AA��BB��AU��AD��BU��BD��8·�źž�����ͼ3�������ʾ�ı�Ƶ��·������4��Ƶ�������źţ�������ļ������ṩ����ʱ���źţ���ͼ3�����ϲ���ʾ�����������ɵ�RS���������Ǽ���(�������)��·�����Եõ���ӳ�ʳ�������A��B�����źŵ����Ⱥ�ķ����ź�A_B_DIR������ʳ���ת��A��ǰB��A_B_DIR=1���ʳ���ת�� B��ǰA��A_B_DIR=0��

����(����)�ź�A_B_DIRһ�������ӵ���ѡһ����ѡ������ѡ�������S0����������A4F_OUT��B4F_OUTѡͨ����ͼ2�Ҳ���ʾ�ļ�����countud���м�������A_B_DIR=1(A��ǰB)ʱ��clk=A4F_OUT(���������)����A_B_DIR=0(B��ǰA)ʱclk= B4F_OUT(���������)��ͬʱ��A_B_DIRҲ���Ƽ��������мӷ�(A_B_DIR=0)�����(A_B_DIR=1)������

ͼ3 �ʳ��ź��ı�Ƶ������·ͼ

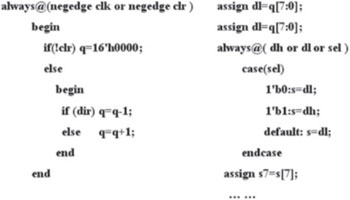

16λ�����Ƽ�/������������Ҫ�����������������ʾ(����Verilog HDL)�����У�clk�Ǽ���ʱ������ˣ�clr���첽����ˣ�dir�ǼӼ��������ƶˣ�dir=1������������dir=0���ӷ�������sel�Ǽ������ݶ�ȡ���ƶˣ��ɵ�Ƭ��������ѡ���ź�ʵ�ָ�8λ����8λ�ļ������������sel=0����8λ��sel=1����8λ��

����¼���ʳ���Ƶ�������������·�ķ������

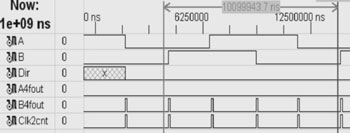

��Xilinx��ISE�����¶Ա�Ƶ��������ģ��jch_4f_dir�ķ��沨��ͼʾ��ͼ4���ò����ǽʳ����������B�ನ�γ�ǰA�ನ��90°ʱ�ķ���������ʱ����Ƶ����ź�B4fout��A(��B)�źŵ�Ƶ�ʳ�4����ϵ������(�������)����ź�Dir=0������ǰ���ԭ��������ȫһ�¡�

ͼ4 B��ǰA���ı�Ƶ���������źŲ���ͼ

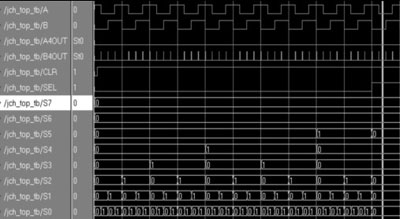

��ModelSim XEIII�����¶Խʳ���ⶥ�������·(������Ƶ������ͼ���)�ķ��沨��ͼʾ��ͼ5���ò����ǽʳ����������B�ನ�γ�ǰA�ನ��90°ʱ�ķ���������ʱ����Ƶ����ź�B4OUT��A(��B)�źŵ�Ƶ�ʳ�4����ϵ���Ǽ�����countud��ʱ�������źţ�����(�������)����ź�A_B_DIR=0�����������ļӼ����������ź�dir=0���������ӷ���������Ƭ���ṩ�����ݶ�ȡѡ���ź�SEL=0��ѡȡ16λ�������ĵ�8λ����������8λ�������Ǽ����������ı�Ƶʱ���źŽ��мӷ������Ľ����

ͼ5 B��ǰA�Ľʳ�������(��Ƶ������ͼ���)����ͼ

��¼���ֳ���ʹ�ʳ�����������ת���������壬������·�������䵽�����������Ĺ��ػ���������п����ֳ�Ӧ��������ɼ������������ֵ����һ����ʼֵN�Ļ����ϱ仯��(�˴���ʹ��30000����0x7530)����ת/��ת�仯�������ڴ˻���������/�����㡣�ʳ�������ת��һȦ����48�����������ֳ��������ݷ�������������·�Խʳ�ת��Ȧ���IJ����dz�ȷ��������0.01%��

����

����һƬXC2C64A-7VC44I����(64���굥Ԫ��33��I/O�ڣ���ҵ��–40°C to +85°C)��Ʋ�ʵ��������¼���ʳ��źŵļ���·������˽ʳ��źŵ��ı�Ƶ�������16λ�����ƼӼ������Լ���MCU���ݶ�ȡ�ӿڵ��ۺϹ��ܡ�¼������ʵ��Ӧ�ñ���������Ƽ���ϵͳ�ṹ��������ϵͳ���ģ��Ӷ������ϵͳ�������ܣ�������¼�����ݲɼ��봫��ϵͳ�У�Ӧ��Ч���ܺá�

�ο����ף�

[1] �غ���. �ۺ�¼���������꾮�����е�Ӧ��[J].����̽�̣�2004��67(6)��59-60

[2] CoolRunner-II CPLD Family Product Specification.http://direct.xilinx.com/bvdocs/publications/ds090.pdf

[3] �ܺ���. ����CoolRunner-II��Ƹ�����ϵͳ[J].���Ӽ�����2003��31(5)��42-44

[4] ���ϵ�.FPGA/CPLD��ƹ���-Xilinx ISE 5.xʹ�����.�����������ʵ�����磬2003

[5] XC2C64A CoolRunner-II CPLD Product Specification.http://direct.xilinx.com/bvdocs/publications/ds311.pdf

���ߣ����ƻ� ��Դ�����Ӳ�Ʒ����

����Ķ�:

- ...2012/03/16 17:13�����ڣ��Уãԣ���������������ѧ�ȣ�̷���ϵͳ���

- ...2012/03/06 14:46�����ڣ��������Ŀ����˶������㷨�Ż�

- ...2011/11/07 15:10������XMEGA128�ı�Яʽ����ʷ��������

- ...2011/10/28 10:27������XML����Ϣ�ҵ����ϵͳ���

- ...2011/10/18 14:27������XMEGA128�ı�Яʽ����ʷ�������Ʒ���

- ...2009/06/02 15:08������Xilinx������CPRIЭ��ʵ�ַ���

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������