����Xilinx������CPRIЭ��ʵ�ַ���

����

Ŀǰ���ֲ�ʽ��վ��Ҫ�������ֿ���ʽ�ӿڱ��������豸�������豸���Ʋ��ַ����CPRI�ӿڣ�Common Public Radio Interface���������л�����������Ƶ�����紫��Ϳ��Ʋ��涼�����OBSAI�ӿڣ�Open Base Station Architecture Initiative������

CPRI��Ҫ���WCDMA����ʵ��������ף�֧�ֳ�����Ericsson����Ϊ��Siemens��Nortel��NEC��Ϊ������OBSAI�ӿ��з���һ���Ѷȣ���������Ը��ӣ�֧�ֳ�����Nokia��Samsung�����ˡ�Alcatel��������ŵȡ����ľ�����CPRIЭ��Ļ����ϣ�������һ����CDMAϵͳ��ʹ��CPRI������Ʒ������������˷��沨�Ρ�

����

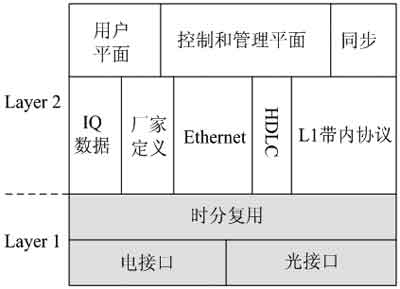

���REC��Radio Equipment Control����RE��Radio Equipment��֮���������RE֮���IQ���ݡ����ƺ������ݼ�ͬ����Ϣ�Ĵ��ͣ�CPRI������L1��L2��Э�飬��ܹ���ͼ1��

ͼ1 CPRIЭ��ܹ���ͼ

ͼ2 CPRI��ϵͳ�е�λ��

��L2���ϣ�CPRI֧�����ֿ���ģʽ��HDLCЭ�����̫��Э�飬���е���Щ��������Ǻ��û������IQ���ݽ�֯��һ����ʱ�ָ��õ���ʽ�ڵ紫�����߹����д��䣬����Э�黹������Ԥ����һ����ʱ϶�������������䳧���Զ������Ϣ��

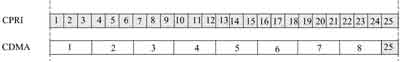

CPRIЭ���֧�������������ʣ��ֱ���614.4Mb/s��1.2288Gb/s��2.4576Gb/s��3.0720Gb/s�����������ָ���ǹ����д����źŵ����ʡ���ΪCPRI��Ҫ�����WCDMA�ƶ��ģ������֡������1/3.84MHz����CDMA����֡Ϊ1/1.2288MHz��Ϊ�˼���CDMA�����ʣ���ʹ��CPRIЭ��ʱ��Ҫ���е��������Է�����25��CPRI֡��ʱ���ڣ��ɷ���8��CDMA����֡��Ϊ�˱������ݵĶ��룬����ͼ3��ӳ���ϵ����ÿ3��CPRI֡��ʱ���ڴ���1��CDMA֡���Ϻ����ĵ�25��CPRI֡��������RSSI��Ϣ�������Ϳ�����CPRI��3������֡��ʵ��CDMA��·�ز��ĸ��ã�����Э�飬�϶��֧��21·�ز��ĸ��á�

����CPRIЭ�飬ÿ256��CPRI֡����һ����֡��ÿ150����֡�ij���Ϊ10ms����Ϊһ������֡��Э��涨ÿ����֡����ʼ�ִ���K�룬����K����ͬ����֡�ͻ���֡�������ݼ����ز��Ϳ����ֵ�λ�ý��н�֡����֡����������в���K28.5����ͬ����ÿ�յ�150��K���־ʱ��ʱ�䳤��Ϊ10ms��

ͼ3 CPRI֡��CDMA֡��ӳ���ϵ

������������ÿ������֡����16���ش��䣬CPRIЭ�����п����λ�ã������û������Զ���Ŀ����֣��������ҵĿ����ֿ��Բ�ͬ��

��ʵ��

CPRI������ϵͳ�е�λ����ͼ2��ʾ��������������ƵĽ���㣬ֱ���������ӣ����й��0����������һ��RE����REC�����1������һ��RE��������в���֧��SERDES IP CORE��Xilinx Virtex5������ÿ��SERDES IP CORE����֧��������ڣ����㼶�����ڽ��նˣ�SERDES����ֱ�ӽ����ת�����������Ĵ��в���ź�ת��Ϊ����������������ָ������Ӧ����·ʱ�ӣ��ڷ��Ͷˣ�SERDES����·ʱ�ӺͲ�������ת��Ϊ���еIJ���ź����������֮�⣬�������ṩ���������е�ͬ��K��ָʾ�������źŴ���ָʾ���������������Լ����Ͷ����ݵ�Ԥ���صȹ��ܡ�

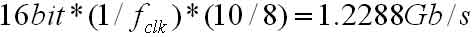

�����в���1.2288Gb/s�Ĵ������ʣ�����Э��涨��֡��ʽ���ó�ʽ1��

���У�fclk����ʱ�ӵĹ���Ƶ�ʣ�֮���Գ��ԣ�10/8������Ϊ�ڲ���ת��ʱ��Ҫ����8B/10B���룬����λ�����ӣ���ʽ1���ʱ��Ƶ��Ϊ61.44MHz�����Ƶ�ʾ���CPRIģ���Լ�SERDES�ο�ʱ�ӵ�Ƶ�ʡ�

1 ������·

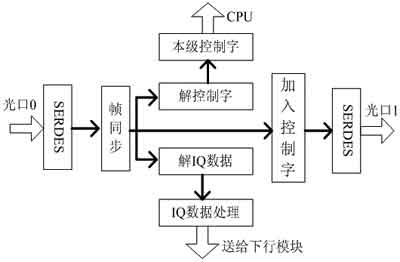

CPRI��������·ģ��Ĺ��ܣ����ڱ���RE����Ҫ����ز��Ϳ����ֵķ��룻������һ��RE����Ҫ��ɻ����źŵ�����

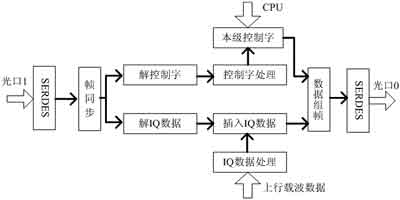

���ݵ����̿�������Ϊ������·ģ��ӹ��0���ջ�������һ��RE�����������ݣ����н�֡����ȡ������RE����Ŀ����ֺ��ز����ݣ����п�����������CPU���ز����ݷ�������RE��������·����ģ�顣���⣬��Ҫ��ɻ������ݵ�ת���������յ��Ļ������ݽ��д�����ͨ�����1ֱ�ӷ�����һ��RE��������·ģ���ͼ��ͼ4��ʾ��

ͼ4 CPRI������·���

֡ͬ��ģ���SERDES�ָ���K����м�����ͬ����10ms����֡��־�������ݴ˱�־ͬ������֡�ͻ���֡��λ�ţ����г�֡��λ�ŷ�Χ��0��149������֡��λ�ŷ�Χ��0��255�������ͬ�������ݷ�Ϊ��·��һ·������RE��ָʾ������ģ���ڶ�Ӧ��λ�ý�������ֺ�IQ���ݣ����п������͵�������CPU��CPU��ȡ������Ҫ�Ŀ����֣����������������ȡ����������IQ��������1CHIP��1.2288MHz�������Բ��еķ�ʽ�͵�������·ģ����д�������һ·ֱ��ͨ�����1����һ��RE������ϵͳ�ļ�����Ҫ�����Լ���RE��ID�Ż��������Ŀ����֡�

2 ������·

CPRI������·ģ����ԱȽϸ��ӣ��ӹ��1������һ��RE���������ݣ�����Ҫ������ݵĽ�֡��������ز��Ϳ����֣���Ҫ���뱾�����е��ز����ݡ�RSSI�Լ����������֣���ͨ�����0�͵���һ��RE����REC����ͬ��������·��������·��ʵ�ֶ����п����ֺ����ݵ�ת�������˱����Ŀ����ֺ����ݣ��������¼�RE�����Ŀ����ֺ����ݣ�������·ģ���ͼ��ͼ5��ʾ��

ͼ5 CPRI������·���

������

ͼ6 �������ݷ��沨��

ͼ7 ���н��10ms��־���沨��

�������ݲ�����ͼ6��ʾ����������SERDES����ת��������ݣ�����֡����16bit��S_rx_slot_cnt=0�������Ϳ����֣�ĩβ��16bit��S_rx_slot_cnt=15������ʹ�ã��ز����ݾ��á�0xaabb����ʾ��

CPRI����ͬ��ģ����150����֡����10ms��־����ʱ���ö�Ӧ��һ����֡�Ŀ�ʼ��ͬ��Ҳ�ǻ���֡�Ŀ�ʼ�����沨����ͼ7��ʾ��

����

�ڽ���������̳�����CPRI��OBSAI�ӿڱ���������ʵ���ϵľ��ü���ԣ�����CPRIЭ����ķֲ�ʽ��վ��Ʒ½���Ƴ������İ���ʵ�ʵ�Ӧ�ó�������ƣ���������CDMAϵͳ��ʵ��CPRIЭ��ķ�����������������ƵĿ�ͼ�ͷ��沨�Σ�����CPRIЭ��������CDMA�ֲ�ʽ��վ�������һ���IJο����塣

����Ķ�:

- ...2012/03/16 17:13�����ڣ��Уãԣ���������������ѧ�ȣ�̷���ϵͳ���

- ...2012/03/06 14:46�����ڣ��������Ŀ����˶������㷨�Ż�

- ...2011/11/07 15:10������XMEGA128�ı�Яʽ����ʷ��������

- ...2011/10/28 10:27������XML����Ϣ�ҵ����ϵͳ���

- ...2011/10/18 14:27������XMEGA128�ı�Яʽ����ʷ�������Ʒ���

- ...2011/08/31 15:12������XC2C64AоƬ������¼���ʳ��źż���·���[ͼ]

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������