����PXIE���ߵĸ���CCD����ͼ��ɼ�ϵͳ���

ժҪ��Ϊʵ�ָ��ٵ����������(CCD)����ͼ��ɼ����䣬���һ�ֻ���PXIE���ߺ�Camera LinkЭ��ĸ���ͼ��ɼ�ϵͳ��Ʒ����������Camera LinkӲ���ӿڵ�·��ʵ������Ƶ�����źŵĽӿ���ơ������źŵĽӿ���ơ�����ͨ���źŽӿ���ƣ�ͬʱ����Xilinx��˾��Vir-tex-5 LX50T��FPGA��ΪPXIE���������������IP�˽����˿�������������Χ��·����Ѷȡ������Ե�����ֱ���ڴ���ʵĹ�����ʽ��PXIE�����ٶȽ����Ż���ʵ����������PXIE����Ϊ8ͨ��ʱ����ȡ�������ʴﵽ1 504 MB��s��д�����ʴﵽ��1 490 MB��s�������������CCD���ݵĴ���Ҫ��

�ؼ��ʣ�PXIE��Camera Link��IP�ˣ�CCD DMA

�����������(Charge Coupled Device��CCD)����20����70�������չ���������Ͱ뵼�����������������������ź���������͡���̬��Χ������Ч�ʺ͵��ת��Ч�ʸߵ��ص㣬��֮���������Ͱ뵼����ϼ����IJ��ϻ��ۺʹ��ģ���ɼ������������ƣ�CCD����Ŀǰ�㷺Ӧ���ڹ��á��������衢��ѧ�о��ȸ������������������������ͼ��ķֱ����Լ������ٶȵ�Ҫ��Խ��Խ�ߣ����ǶԸ���ͼ��ɼ�ϵͳ�����ܡ��ȶ��ԺͿɿ���Ҳ������µ�Ҫ���������һ�ֻ���PXIE���ߺ�Camera LinkЭ��ĸ���CCDͼ��ɼ�ϵͳ��Ʒ���������ϸ˵���˲���ģ��ľ���ʵ�ַ�ʽ��

1 ϵͳ����ԭ�����������

1��1 Camera LinkЭ�鼰PXIEЭ�����

(1)Camera Link����

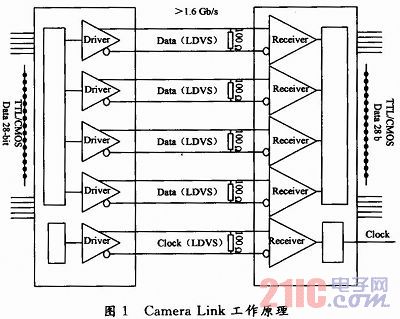

Camera Link��һ�ֻ�����ƵӦ�÷�չ������ͨ�Žӿڡ�����NI��13�ҹ�˾����Channel Link���������Ƴ���һ�����ͽӿڣ���������������豸�����ӡ�Camera Link�������˽�28λ����������7��1��ʽת��Ϊ4��LVDS��������1��LVDSʱ���źţ����з��������ն˽��д�������ϸߴ������ʿɴ�2��38 Gb��s��ͼ1ΪCamera Link����ԭ��ͼ��

Camera Link�ӿ�Э���ṩ4���źţ���������źš�ͼ�������źš���Դ�ʹ���ͨ���źš���ӿ���3�ֽṹ���ֱ��dz�������(Base)���м�����(Medium)������(Full)��Camera Linkʹ�ö˿ڶ�����������Щ���á�3M 26-pin MDR(Mini D Ribbon)������֮���Ա�ѡ����Camera Link����ʹ������Ϊ���������ƺ���ǰChannel Link���ٴ���ijɹ����顣

(2)PXIE����

PXI(PCI Express for Instrumentation)��NI��˾��1997�����������PXIE����Compact PCI����������ʱ�Ӻ�ͬ���������ߣ����������Ȼ��PCI���ߡ�PXI Express���PXI�������ĸĽ������ƾ�����������PCI Express���ص㣬���ô��д��䣬�㵽����������˽ṹ����ͬ��PXI�����������豸�����������PXI ExpressΪÿһ���豸�ṩ�����Ĵ���ͨ����ͬʱ�������ӵ�ʱ�Ӻ�ͬ�������ź��Լ�ӵ������Ľӿ���������ʹ�����ڲ�����ͨ�š���ҵ�Զ���������ӵ�и���ļ������ơ����IJ���PXIE-8x���ϸߴ����ٶȴﵽ1400Mb��s��

1��2 �������

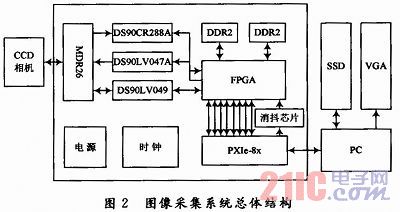

ϵͳ����ṹͼ����ͼ2��ʾ��

ͼ2�У�DS90CR288AΪNI��˾�����ܴ���ת��������Camera Link�ӿ�Э���4·LVDS�źź�1·LVDSʱ��ת��Ϊ28λLVCMOS��LVTTL���ݺ�һ·ʱ���źţ�DS90LV047AΪNI��˾��3 VLVDS 4·����ת�����������DS90LV049ΪNI��˾��3V LVDS˫����·��������˫����·��������

ϵͳ��������Ϊ��

���ȣ��ɼ���ͨ��DS90LV047A��CCD��������Ŀ���ָ�CCD����ڽӵ�ָ����ɼ�����ͼ�����ݷ�Ϊ4·LVDS�����źź�1·LVDSʱ���źţ�ͨ���ӿ�������MDR26�����͵�ͼ��ɼ�����ͼ��ɼ�������������ת����38·�����źź�1·��·ʱ�Ӵ���FPGA�������ݴ����������������ܴ�Ϊ��֤���ݵ������ʼ���߿ɿ��ԣ�ʹ����2��Micron 2 GB DDR2�����ݽ��л����ƹ�Ҵ�����FPGA�����û���������и��ٵ�ͼ�������ɼ���ͨ��PXIE-8x��ͼ�������ϴ���PC(��λ��)�Ͻ��к��ڴ�����ͬʱʵ��PC(��λ��)��ͼ��ɼ����Ŀ��ơ�ͼ�����ݽ���ͨ��PC�����ݴ洢��SSD(Solid-state Drive)�������ϣ��Թ���ʱ���á��ڶ���д�ٶȵȹؼ������ϣ�SSD������ԶԶ���ڴ�ͳ��еӲ�̣����ѡ��SSD������Ϊ���ݴ洢���ʡ��ɼ���������DS90LV049(LVDS˫��·������������˫��·������)��ʵ�ֲɼ����������Ĵ���ͨ�ţ��û����Ը�����Ҫ��CCD����������á�

2 �ؼ�ģ�����

2��1 Camera Link�ӿ����

����ϵͳ����Ҫ��Camera Link�ӿ���ư���3�����֣���Ϊ��Ƶ�����źŽӿ���ƣ������źŽӿ���ƣ�����ͨ������ӿ���ơ�

2��1��1 ��Ƶ�����źŵĽӿ����

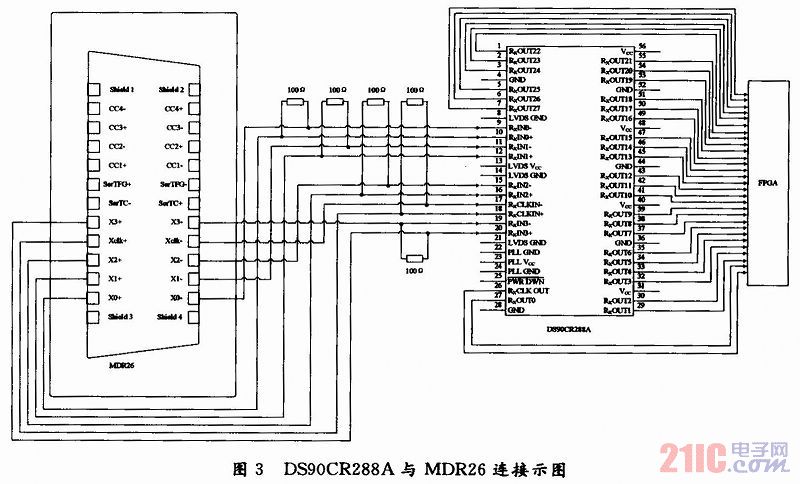

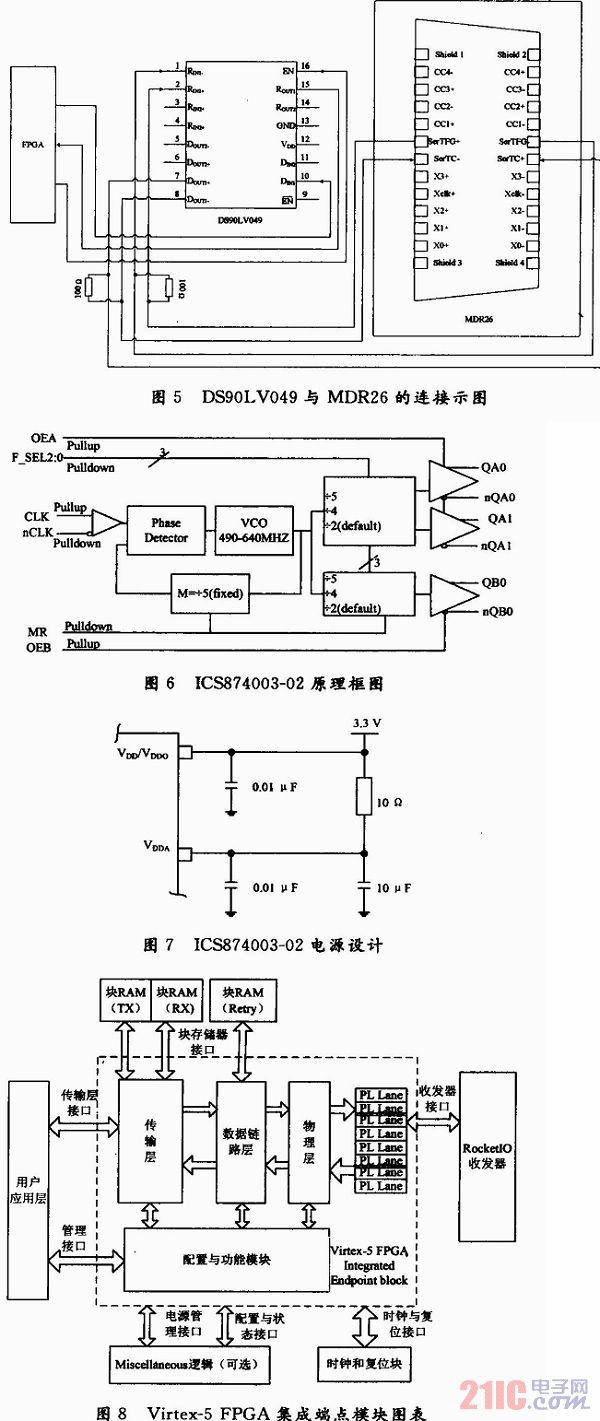

��Ƶ�����ź�ΪFVAI��LVAL��DVAL��SP�����Ƿֱ���֡�����źš��������źš����������źźͱ����źţ�4·��ΪLVDS�����źţ����1��LVDSʱ���źţ��ڴ˲�����National Semiconductor��˾��DS90CR288AоƬ����5·LVDS�ź�ת��Ϊ28·�����źš���������ͼ��ͼ3��ʾ��

2��1��2 �����źŽӿ����

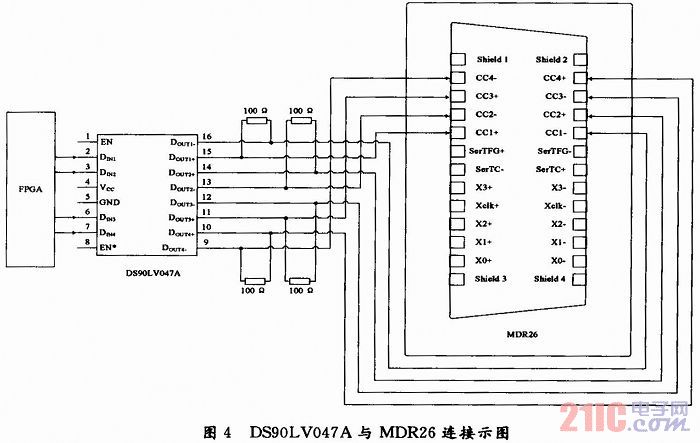

��������ź�CC1��CC2��CC3��CC4Ϊ4·LVDS�źţ�Ϊ��ʡ���߿ռ䣬FPGA�����Ŀ����źž�Ϊ�����źţ���˲���National Semicon-ductor��˾��DS90LV047AоƬ���ɼ��������ĵ���COMS�����ź�ת��ΪLVDS�źţ���ɶ�CCD����Ŀ��ơ�ͼ4ΪDS90LV047A��MDR26�����ӡ�

2��1��3 ����ͨ���źŽӿ����

����ͨ���ź�������LVDS�ź��ṩ����Щ�ź�ʹ�������ʹ����֮����Խ���ͨ�š���Ϊ��˫��ͨ�ţ��ڴ˲�����National Semicon-ductor��˾��DS90LV049оƬʵ����LVDS����źŵ�����CMOS�źŵ�˫��ת����ͼ5ΪDS90LV049��MDR26������ʾͼ��ͼ��ENΪ1ʱ��EN���Բ��ӣ�4��ͨ·����ȫͨ��

2��2 PXIEģ�����

2��2��1 PXIE��ʱ�ӵ�·���

��PXIE�淶�У�����ʱ�ӵ�Ƶ���ȶ���Ҫ����100 MHz±300 ppm������(Cycle-to-Cycle)��ҪС��125 ps��ռ�ձ�Ҫ��50��±5�����ڡ���ˣ�ϵͳ��ѡ��IDT��˾��ICS874003-02��Ϊ100 MHz�ο�ʱ�ӵĶ���˥������ICS874003-02��һ������ܵĽ����ʱ��ת��ΪLVDS��ƽʱ���źŵ�ʱ�Ӷ���˥��������Ԫ����֧��PXI Expressϵͳ������˥����“���”100 MHz PXIE����ʱ�Ӷ�����ͬʱ����ת����250 MHz LVDS���������ʱ��������ICS874003-02��оƬ�ڲ�������һ�������ܣ�����������������ļ������Ϊ400 kHz�����Կ�������ʱ�ӣ���С������������֧�ֵ���1 ps RMS������λ�����Ļ�ʱ�����ɣ��������PXIE�ĸ���Ӧ�õ��ϸ�Ķ���Ҫ�����Ľϴ����ڶ���Ϊ35 ps��ռ�ձȱ仯Ϊ50��±2������ȫ��������PXIE��ʱ�ӵ�Ҫ�����ڲ�ԭ��ͼ��ͼ6��ʾ��

��ϵͳ����в���QA0��nQA0��QA1��nQA1���Բ�����ʱ�ӣ����ҽ������������Ƶ���ķ�Ƶϵ������Ϊ5��ʹ���ʱ��Ƶ�ʺ�����ʱ��Ƶ����ͬ��

ICS874003-02�ṩ�����ĵ�Դ���Ը����ڲ���������Ŀ���������VDD��VDDA���Լ�VDDO�ֱ��뵥��ͨ���������ӵ���Դ�㣬������ÿ����Դ���϶�Ҫ������·���ݣ�Ϊ�˻�ýϼѵ�ʱ�Ӷ������ԣ���Դ��Ҫ����롣��ͼ7��ʾ��1��10 Ω�ĵ����Լ�1��10 μF��0��01 μF����·���ݹ�����һ����Դ�˲���·�����ӵ�ÿ��VDDA�ţ�10 Ω�ĵ�����Ա������������

2��2��2 PXIE��IP core���

��ϵͳ�У�����Virtex-5LX50T��FPGA��ΪPXIE�Ĵ��������������FPGA�ڲ�������PCIe�˵�ģ�飬���Լ����˺ܶ���ΧӲ����·������Ѷȡ�PCIe�˵�ģ���IP�˿�ͼ��ͼ8��ʾ��

��ͼ8���Կ�����PXIE IP�˲��÷ֲ�ṹ�����ֱ�Ϊ��������·ģ�顢�����㡢������·�㡢�������û�Ӧ�ò㡣����㸺�����û�Ӧ�ò�(User Applieation)�ṩ�Ĵ�����(TLP)�������䴫�䡣������·�㸺����·���������������ԣ���������ļ��;����������㸺����ɰ��ij�֡�ͽ�֡���ֽڵ���ϺͲ�֡���·�ij�ʼ����ѵ�����������ɺͽ��š�����ʱ����������·ģ�鸺�����������ɵ�����Ӧ�õ����������У�ͬʱ���õ�������ģ����յ��������У��Ϻ�Ѱ����������ӿڣ�����ʱ������Ӵ���ӿ��Ͻ���TLP�ֽڣ��������н����������ҽ�DLLP��TLP���š�

2��2��3 PXIE�����ٶ����⼰������

����PXIE����Э���ǻ���PCIe����Э�����չ�����Կ�������Ŀǰ�Ƚϳ����PCIe����Э��ʵ�ּ�����Ӳ��������Ʋ����ʵ��PXIE����Э�飬����PXIEЭ���һЩ��չ�ӿڣ���������FPGA��Χ�û���Ӳ����·����ʵ�֡�FPGA��������Xilinx��˾�ṩ��һ�׳��죬�ȶ�������ѵ�PCIe���䷽������IP(Intellectual Property)����ʽ�ṩ���û���

PCIe IP����ȻΪPXIE����Э���ṩ�˽��������������Ȼ�������⡣���ȣ���ʵ�ʲ��Թ��̵��У�����PCIe IPһֱռ����CPU��ʹ��PC�ڽ������ݴ���ʱ����������

����Ķ�:

- ...2015/02/12 15:10������PSO-LSSVM�ij���ʱ��ˮ��Ԥ��

- ...2014/12/31 13:14�����ڣУ��������������������˴�����Ʋ���

- ...2013/12/18 10:49������PCI-9846�������������Լ������о���ʵ��

- ...2013/12/10 10:49������PCI-9846H������ʱ������ĵ�ѹ���λ�����о�

- ...2012/12/26 10:33������PCI-9846�ı�Ƶ��������ܲ���ϵͳ

- ...2012/04/27 10:12�����ڣУã����ˣƣã� �Ĵ������ͻ��������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������