��Դ���С��ʿ 41��DDR �ڴ��Դ

���ߣ�Robert Kollman���������� (TI)

CMOS ��ϵͳ�Ĺ�����Ҫ��ʱ��Ƶ�ʡ�ϵͳ�ڸ�դ������������Լ���Դ��ѹ�йء���������ߴ��С��Դ��ѹҲ��֮���ͣ��Ӷ���դ�������ġ����ֵ͵�ѹ����ӵ�и��͵Ĺ��ĺ��ߵ������ٶȣ�����ϵͳʱ��Ƶ��������ǧ���ȼ�������Щ��ʱ��Ƶ���£��迹���ơ���ȷ��������ֹ�ͽ�С������ϣ������߱���ȵ�ʱ���źš���ͳ�ϣ���ϵͳ����һ��ʱ���ص����ݼ�ʱ����˫���������� (DDR) �ڴ�ͬʱ��ʱ�ӵ�ǰ�غ��½��ؼ�ʱ����ʹ����ͨ���ٶȷ���һ������ϵͳ�������Ӽ��١�

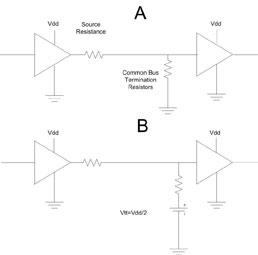

����������Ҫ��ʱ�ӷ����������Ҫ����С�ģ��Դ�����С������ͷ���ЧӦ��������ܻᵼ�¶��������������ʱ��ͼ 1 ��ʾ�����ֱ�ѡ������ֹ��������һ�ַ�����A���У�������ֹ�����������ڷ��������ĩ�ˣ����������ӵء�����������������ڵ�̬�£��������Ĺ��ı�Ϊ�㡣�ڸ�̬��ʱ�����������ĵ��ڵ�Դ��ѹ��VDD��ƽ���������ߵ��裨Դ�迹�Ӷ˽ӵ��裩��ƽ������Ϊ��Դ��ѹƽ�������������ߵ��衣

ͼ 1 VTT �˽ӵ�ѹ����һ��˽ӹ���

�ڶ��ַ�����B���У��˽ӵ�������������Դ��ѹ (VTT)����Դ��ѹΪ VDD ��ѹ��һ�롣���������ĺ㶨�������Դ��ѹ�أ������ VTT����Vdd/2����ƽ�����Զ˽ӵ��衣��ȵ�һ�ַ��������ַ��������Ĺ��Ľ�Ϊ�� 1/2������Ҫ����һ����Դ��ͬʱ�����Ե�Դ��Ҫ����Щ�ر����ȣ��������ҪΪ��������ѹ (VDD)��һ�룻��Σ�����Ҫͬʱ��������ͼ�ȡ�������������������ѹΪ��ʱ���������� VTT ��Դ��Ȼ������������Ϊ�ߵ�ƽʱ�����������Դ���Ϻ�Դ����Ҫ��ϵͳ���ݱ仯ʱ�ڸ�ģʽ֮��ת�����ұ����ṩ��Դ�迹��ֱ���ӽ�ϵͳ��ʱ�����ʡ�

���ݶ˽ӵ��衢ʱ��Ƶ�ʺ�ϵͳ���ݣ�ȷ����ֵ����������ס�����ƽ������Ҫ������һ�㣬�����Ա� 1/10 ��ֵ���ĵͺü���������ϵͳΪ��̬��û�������̶������ʱ���ʣ�����ÿ�����ڶ������ݼ�ʱ�����һ���һЩ��̬���������������Ҫ����������Щ���ء�

ƽ����������֤ϵͳ������һ����Ҫ��ֵ����Ϊ����ȷ����ȷ�ĵ�Դ���˺���Ҫ�����磬�����ܻ��ڿ���ʽ��Դ���ĺ�������ѹ���ĵͳɱ���С���֮�����Ȩ�⡣�� 1 ��ʾ�˿���ʽ��Դ��������ѹ���������Ŀ�����Ҫ���ĺͳɱ��ȷ���ĶԱ�������ñ������ڿ���� 3 ����ֵ������һЩ��ѹ������Ȥ���ǣ������ֵ����һֱ���ڵĻ����ͺ��Ѵ����߹��ġ����� DC ������������������ȷ��ѡ�����ԣ��Ӹ�������������������ѹ�����Ǹ��ѵ�ѡ��

�� 1 ���Է��������С���ɱ����͵����翪��ʽ��Դ��Ч��