Xilinx Zynq-7000 EPPΪ���¿�����ʱ��

��������˼Zynq-7000 ����չ����ƽ̨��EPP����˫ ARM Cortex-A9 MPCore ������ϵͳ��ɱ������Ӳ IP ������ܼ�����һ���ṩ������ԡ��������Ժ����ܵ�������ϡ�Χ����ո��Ƴ��Ŀ���չ����ƽ̨��EPP���� ����˼�ڽ���3�·����˻���Zynq -7000��ϵ�е�����������

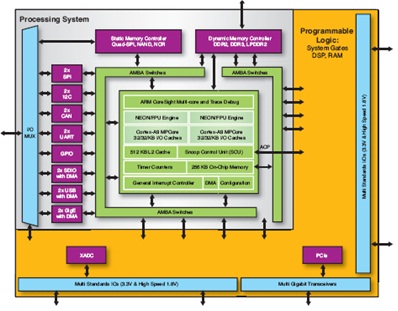

�������� 28 nm���칤�գ� Zynq-7000Ƕ��ʽ����ƽ̨ϵ�е�ÿ���Ʒ�����ô���NEON��˫���ȸ��������˫�� ARM Cortex-A9 MPCore ����ϵͳ����ϵͳͨ��Ӳ��������˰���L1��L2 ���桢�洢���������Լ������������ڵ�ȫ�漯�ɡ�(ͼ 1)������ FPGA ���̴�ǰ���Ƴ�����Ӳ�˻����˴��������������� Zynq-7000 EPP �Ķ���֮����������ARM������ϵͳ���ǿɱ����Ԫ�������п��ơ�Ҳ����˵������ϵͳ�ܹ��ڿ���ʱ�������� FPGA ��֮ǰ�������и��������ڿɱ����֮��IJ���ϵͳ�����������Ա�ͿɶԴ���ϵͳ���б�̣�������Ҫ�����ÿɱ������

�����������ַ������������ģʽ����ȫ���ܱ� ARM ������Ƭ��ϵͳ��SoC�������¡���ȥ���ʦ��Ҫ�� FPGA �����б��������Ƭ�ϴ��������Ǿ���ζ�������Ҫʹ��������������� FPGA ���ʦ��������ʹ�� Zynq-7000 EPP������ȫ���ص�����һ���⡣

ͼ 1 —— ��ͬ�������� FPGA �ܹ���Ƕ�� MPU ��

����˼ȫ�� Zynq-7000 EPP ϵ��ʹ�� ARM ���������ǿɱ���������п��ơ�

����ͼ1�����֣�

�����²�Ʒϵ���������ӳٺʹ�ͷ���оƬ�ķ��գ�����ζ��ϵͳ����Ŷӿ����������Ƚ��ĸ���Ӳ����̶���Լ����ٴ���������Ƭ��ϵͳ�������������κΰ뵼����������ʵ�ֵġ�������Zynq -7000 EPP �ܹ�Ϊ���Ĵ����ߴ�����������洦��������רҵ��Ӳ����������ϵͳ���ʦ����ǵ�����“������”�����Ƕ�����̽�ִ���������������ϵĿ����ԣ�������������δ������Ĵ���Ӧ�á�

��������˼����ƽ̨���ܲ� Larry Getman ��ʾ��“�ӽϸ����IJ����˵��Zynq-7000 EPP Ӧ������һ��ȫ�µİ뵼���Ʒ�����Ȳ��ǵ����Ĵ�������Ҳ���ǵ����� FPGA�����ǵIJ�Ʒ�����ߵ�������ϣ�����������Dz��ܹ��������������н�������ľ����ԣ��������˫оƬ��������� ASIC��

����Getman �Ƶ�ǰ���������ϵͳ���ǽ�һ��FPGA��һ����������������һ������Ƭ�ϴ�������ASIC��ͬһ��PCB�����ʹ�á�����˼�Ľ��²�Ʒ��֧��ʹ������˫оƬ��������Ĺ�˾����һ��Zynq-7000 оƬ��������һ��ϵͳ����ʡ�����ϳɱ��� PCB �ռ䣬���ҽ��������幦��Ԥ�㡣���ڴ�������FPGA ����ͬ�ļܹ��ϣ��������Ҳ�õ��˴��������

����Getman ��ʾ Zynq-7000 EPP ����ӿ�� ASIC�� FPGA ���г�Ǩ�ơ����ý������칤��ʵʩ ASIC ���ڰ����ҶԴ����Ӧ����˵����̫����ˣ�Խ��Խ��Ĺ�˾������ FPGA�����ೢ�Լ��ؾ� ASIC �����Ĺ�˾���þɵ����칤����ʵʩ���ǵ���ƣ�����ʦ��֮Ϊ“��ֵ��֪��Ƭ��ϵͳ ASIC”��Ȼ�� ASIC ������Ҫ�ϳ���������ڲ��Ҵ���������ƣ�respin���ķ��գ�����һ�����ý���dz������ҿ��ܻ����ӳٲ�Ʒ������ʱ�䡣Getman ˵��“��ɼ�����ȣ��������� 28 nm������ Zynq-7000 EPP�������Ŀɱ�������ֲ������ڳߴ��������ĵ����⣬�������ڴ�����ϵͳ�л��Ӳ�� 28 nmƬ��ϵͳ�ĸ������ơ�ƾ�費�� 15 ��Ԫ����ʼ�ۼۣ�����ʹ�����Щ�������Ǻܴ�� ASIC �ڳɱ��ͷ����϶����ٻ��㡣�����Լ�����������Ӳ���Ŷӿ���������Щ����ASIC ������ŶӾͺ���������һ�㡣”

����Getman ��ʾ�Դ�����˼ȥ���Ƴ����ܹ��������г���Zynq-7000 EPP����Ȥ������dz�ǿ�ҡ���ѡ�����һ�����������ÿͻ���alpha customer���ѿ�ʼ�Խ�ʹ�� Zynq-7000 ������ϵͳ����ԭ����ơ��ü����dz������˷ܡ�”

�������ܼܹ�����

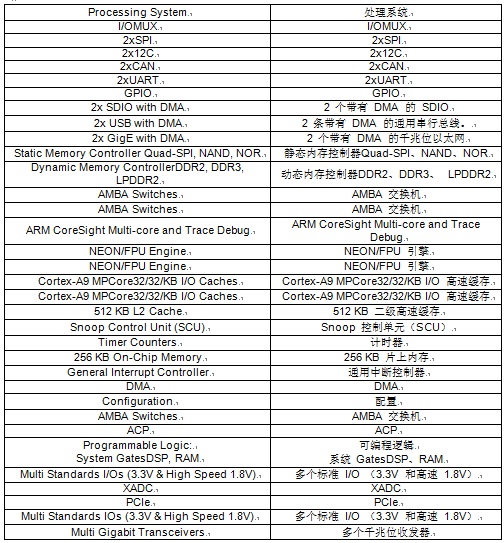

����������˼��������������ܲ� Vidya Rajagopalan ���쵼�£�Zynq-7000 EPP ����Ŷ�ר������������������Ƴ���һ����ƾ����ļܹ�������ѡ��Ӧ�ù㷺�ұ��ܻ�ӭ�� ARM ������ϵͳ���⣬����Ŷӵ�һ����Ҫ�ܹ��������ڴ���ϵͳ�Ϳɱ����֮��㷺ʹ�øߴ��� AMBA® ����չ�ӿڣ�AXI™������������һ�����ܹ��Խϵ͵Ĺ���֧�� ARM ˫�� Cortex-A9 MPCore ������ϵͳ�Ϳɱ����֮��Ķ�ǧ��λ���ݴ��䣬���������˿��ơ����ݡ�I/O ���ڴ������ٵ�����ƿ����

����ʵ���ϣ�����˼һֱ�� ARM ���ֽ��ܺ����������� ARM �ܹ������ʺ��� FPGA Ӧ�á�Rajagopalan �ƣ�“AXI4 ӵ�д洢�����ʰ汾�������ݷ��ʰ汾������˼�ƶ��� ARM �������壬��Ϊ�������Ӧ�ö����������� IP ������ߴ�����Ƶ����Ϊ�� IP��ARM �IJ�Ʒû���������ӿڣ��������ѡ�������Ǻ�����”

����Getman �����ܹ�����һ����Ҫ����������˼��һ������ı��ӿ� IP Ӳ���� Zynq-7000 EPP оƬ�С���˵��“���Ǿ���ѡ��Ӧ�ø��㷺�����裬���� USB����̫����SDIO��UART��SPI��I2C �� GPIO ���DZ����á�����һ�����⣬�Ǿ������ǻ�������������� CAN��CAN ������רҵ����Ӳ������֮һ������������������ҪĿ���г���Ӧ�ù㷺����ҵ������ҵ������Ӳ����������ֻ�� Zynq-7000 EPP ����һ�����㡣

�������ڴ淽�棬Zynq-7000 �����ṩ�˶�� 512 KB �Ķ������棬������������������Getman ˵��“Zynq-7000 EPP �������� 256 KB �ĸ����ݴ��������Ǵ������� FPGA �����Է��ʵĹ����ڴ档”

����һ�������Ķ�� DDR ��������֧���������͵�˫�����������ڴ档 Rajagopalan ��ʾ��“����� ASSP ��Ŀ�����ض�ϸ���г��������ǵ�Ŀ���� LP DDR2��DDR2 �� DDR3������û����Ը������������ڹ��ʺ�����֮������Ȩ�⡣����һ�ֶ�� DDR ���������������ǽ����ṩ���ƿ������Ĺ�˾֮һ��”

����Zynq-7000 EPP ������һ����������Ҳ������˼�Ľ������ƽ̨�� ���뿪���塢������IP ���ĵ�һ���ṩ���������ͻ�Ѹ�����ֺ����С����⣬����˼������δ�������в����Ƴ�����ض���ֱ�г����ض�Ӧ�õ� Zynq-7000 EPP ���ƽ̨�������忨���ӿ���IP ���ĵ�������������ŶӼӿ��Ʒ�����ٶȣ�����ġ�Xcell �ڿ����� 68 �ڷ�����£�http://www.xilinx.com/pub-lications/archives/xcell/Xcell68.pdf����

��������˼���˼ƻ���Ա�� ARM ����Ҳ��Ϊ�ͻ��ṩ�ḻ�� Zynq-7000 EPP ��Դ��������������ϵͳ�����Գ���IP���ο���Ƽ�����ѧϰ�Ϳ������ϵȡ�

�������˴����ɫ��оƬ�������ߣ�����˼��Ϊ Zynq-7000 EPP �����ṩ�˼����õ���ƺͱ�����̡�

�����Դ�����Ϊ���ĵĿ�������

����Zynq-7000 EPP ������һ�ֳ����Ĺ�������Ƕ��ʽ������Ӳ������ʦ��������һ��������ִ�п��������Ժ�ʵʩ�����䷽�������ڷdz����ƣ�������ͨ�� Xilinx® ISE® �����װ�͵����������ṩ�ij���Ƕ��ʽ��Ʒ�����ͼ 2����Getman ע�������Ӧ�ù���ʦ��ʹ������֮ǰ������в��õ���ͬ�������ߡ�����˼ΪǶ��ʽ����Ӧ����Ŀ�ṩ�������������߰���SDK��һ�ֻ��� Eclipse �Ĺ�����װ��������ʦ������ʹ�õ������������������� ARM Development Studio 5 (DS-5™)��ARM RealView Development Suite (RVDS™) ���κ��������� ARM ��ϵ�Ŀ������ߡ�

����Linux Ӧ�ÿ�����Ա���Գ������ Zynq-7000 �����е����� Cortex-A9 CPU �ںˣ��ڶԳƶദ����ģʽ��ʵ�ֽϸߵ����ܡ����⣬���ǻ������ڵ���������Գƶദ����ģʽ�����е� Linux ϵͳ��һ��ʵʱ����ϵͳ (RTOS)������ VxWorks �ȣ������� CPU �ںˣ�Ҳ�����ڶ�����ͬʱ���á�Ϊ��֧�ֿ��ٿ�ʼ��������������˼Ϊ�ͻ��ṩ�˿�Դ�� Linux ��������������������������������Χ�����豸��USB����̫����SDIO��UART��CAN��SPI��I2C �� GPIO��������˼�� ARM ���������̬ϵͳ���ṩ��ȫ��֧�ֵ� OS/RTOS �忨֧�������Լ��м����Ӧ��������

�������ͬʱ��ISE �����װ�е�Ӳ�����������Ƕ��ʽ����������������ƣ���Ϊ����չ����ƽ̨������һЩ�²��衣������ϵͳ��һ��ӵ������ͨ����Χ�豸��������˫��ϵͳ��Ӳ�����ʦ����ͨ���ڿɱ������Ϊ������ϵͳ���Ӹ����� IP ��Χ�豸������չ�䴦��������Ӳ���������� Xilinx Platform Studio ʵ�������ೣ��Ӳ������������Զ���������Э�����ʦ�Ż��������š�Getman ����˵��“���ǻ�Ϊ ISE ������һЩ��Ӳ���ϵ�ͽ��津�����й�ͬ���ԵĹ��ܡ���������˵������Ҫ����ҪΪ����������Ա��Ӳ�����ʦ���ṩ���ʵĿ���������”

����һ�����Ƶı�̷���

����������˼�IJ�Ʒ�У��û��������ÿɱ��������ͨ�� AXI “����”ģ�齫�����ӵ� ARM �ںˣ�����չ������ϵͳ�����ܺ��ܷ�Χ������˼�� ARM ���������̬ϵͳ�ṩ�˴������� AMBA �ӿ� IP �ںˣ��������Ա�� FPGA �ɱ������ʹ�á������Ա������������������Ŀ��Ӧ��������κ��Զ��幦�ܡ�����ʹ�õ����� 7 ϵ�� FPGA ��ͬ�ij����ɱ�����ṹ�����������Ա���Լ���һ�����߶�������ļ����������ò��ֿ������ü�������֧���������輴ʱ�Կɱ�������ܽ������±�̡�

��������������֮��Ļ����������������Ա�ںܴ�̶��������ġ�

����Ķ�:

- ...2011/03/25 10:57����Multisim�����ж�Xilinx �ɱ�����豸���б��

- ...2009/06/02 16:43��Xilinx FPGA�Ĺ����Ż����

- ...2009/06/02 15:08������Xilinx������CPRIЭ��ʵ�ַ���

- ...2008/08/15 15:42��Xilinx�ͳɱ���ʾ���������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������