Xilinx FPGA�Ĺ����Ż����

����FPGA��˵�������Ա���Գ��������ɱ�������Լ���صĹ�����ȷ���㹦�ģ�Ȼ����ͨ���Ż�������ʹFPGA����Լ���Ӧ��PCB���ڹ��ʷ���Ч�ʸ��ߡ�

��̬�Ͷ�̬���ļ���仯

��90nm����ʱ������й©�����ASIC��FPGA������൱���ء���65nm�����£���һ���������ս�ԡ�Ϊ��ø��ߵľ�������ܣ����뽵����ֵ��ѹ����ͬʱҲ�Ӵ��˵���й©��Xilinx��˾�ڽ��͵���й©������������Ŭ����������ˣ�Դ��й©�ľ�̬�����ڽϲ�͵����������µı仯��Ȼ��2:1��й©�������ں˵�ѹ��VCCINT����Ӱ��ܴ�Լ���������ɱ���������VCCINT������5%����̬���ľͻ����Լ15%���Ϻ�й©��������ᣨ��оƬ����������ء�

FPGA�о�̬���ĵ�������Դ�ǹ�����·��ֱ�����������ںܴ�̶��ϣ��ⲿ�ֵ����湤�պ��¶ȵı仯��������I/O��Դ����HSTL��SSTL��LVDS��I/O���Ķ˽ӵ�ѹ���Լ�LVDS�ȵ���������I/O��ֱ����������ЩFPGAģ��ģ��Ҳ������̬���ģ���ͬ���빤�պ��¶ȵĹ�ϵ�������磬Xilinx FPGA����������ʱ�ӵ�����ʱ�ӹ�������DCM����Xilinx Virtex-5 FPGA�е������PLL�����Լ�Xilinx FPGA����������������Ϣ�ɱ���ӳٵĵ�ԪIODELAY��

��̬������ָFPGA�ں˻�I/O�Ŀ��ػ����Ĺ��ġ�Ϊ���㶯̬���ģ�����֪�����ؾ���ܺ����ߵ����������ݺͿ���Ƶ�ʡ�FPGA�У�������ڽ�������ʵ�����Ϳɱ�̻������������������ܼ������ݺͽ��������ߵ��ݡ�

��̬���ʵĹ�ʽ��PDYNAMIC=nCV2f�����У�n=���ؽ���������C=���ݣ�V=��ѹ�ڷ���f=����Ƶ�ʡ�

�����յ�����װ��ͨ���ڲ�FPGA�ܹ��ı䣩���Լ��ٿ��ؾ���ܵ����������ø�С�ߴ�ľ���ܿ������̾����֮������߳��ȣ��Ӷ����Ͷ�̬���ʡ���ˣ�Virtex-5 FPGA�е�65nm�����դ�����ݸ�С�������߳���Ҳ���̡����߽�������ɽ����ĵ��ݼ�СԼ15%��20%����ɽ�һ�����Ͷ�̬���ʡ�

��ѹ���ڶ�̬����Ҳ��Ӱ�졣��90nmת��65nm���գ�����ͨ����VCCINT��1.2V����1V��Virtex-5 FPGA��ƵĶ�̬���ʾͽ�����Լ30%���ټ��Ͻṹ��ǿ�����Ĺ��ʽ��ͣ��ܵĶ�̬���ı�90nm����ʱ���ʹ�40%��50%��

��ע����̬������VCCINT��ƽ�������ȣ�������FPGA�ں���˵���������¶Ⱥ����ء���

����FPGA��Ƽ���������

Xilinx��˾�ṩ������ʷ������ߡ�XPower Estimator (XPE)�������ݱ����߿��������Աʹ������ʵʩ����ǰʹ�á����������ʵʩ��ɺ�����Բ��õڶ����XPower Analyzer����������ĸı�Թ��ĵ�Ӱ�졣

�����ĵ�һ�ַ�������Ϊ���ѡ������õ�FPGA��Ȼ��������ɱ��������һ���Ż���ƵĹ��ġ���ȷ�����ѡ���ͬʱ���ƾ�̬�Ͷ�̬���ġ�

Դ��й©�����ľ�̬��������������Դ��������Ҳ����˵�����ڹ����ض�FPGA��ʹ�õľ������������ˣ����������ʹ�õ�FPGA��Դ�����ø�С������ʵ����ƣ���ô�Ϳ��Խ��;�̬���ġ�

���Բ��ö��ַ�����������ƵĹ�ģ���ϻ�����һ�ּ��ɾ��������ܷ�ʱ��Ҳ����˵����������·���һ�����Թ��ܣ����ұ˴���ȫ��ͬ����ô�Ϳ���ֻ��һ���·�����������һ�������ͬ���Ĺ��ܡ�������Ҫ������Դ�ͼ�����һ�롣

��һ����С����ģ�ķ���������Xilinx FPGA�IJ��������ù��ܣ��������ֵ�·��ͬʱ����ʱ��������ij��ʱ��ν�ij���ֵ�·��������ʵ����һ�ֵ�·���ܡ�

ͬʱ�������Խ������ƶ�����̫�����Ƶ���Դ�����磬��״̬��ת�Ƶ�BRAM�����߽�������ת�Ƶ�DSP48ģ�顢�Ĵ���ת�Ƶ���λ�Ĵ��������Լ���BRAMת�Ƶ����ұ�RAM��LUTRAM����ͬʱ�����Ա�֤��Ҫ����Ƶ�ʱ��̫���ţ���Ϊ��������Ҫ��������ͼĴ�����

���⣬��Ӧ����ַ���FPGA�ܹ��м��ɵ�ӲIP�飨BRAM��DSP��FIFO��Ethernet MAC��PCI Express�����ŵ㡣

���;�̬���ʵ���һ����������ϸ�����ƣ����������ֱ������Դ������о�����ʹ�õ����ж��������DCM��PLL��ģ�飬�������������ģ����ƺ����ǽ��������Դȥ���������ڹ�����һ����Ʒʱʹ����һЩ�������롣��DCM��PLL������ƵĶ��㣬����ģ��֮��Ϳ��Թ�����Դ���Ӷ��ɽ�һ����С��ƵĹ�ģ������ֱ�����ʡ�

���õ�ʹ�ô洢��ģ��Ҳ�ɰ�������FPGA��ƵĶ�̬���ģ��Ӷ���һ���������幦�ġ����ڶ�̬�������ݿ�������ȣ���Ƶ�ʵĺ��������Ӧ���������з��ʿ�洢���ķ�ʽ��ȷ���ܹ����ݿ���Ƶ�ʽ����Ż�������

Xilinx FPGA�ṩ�������͵Ĵ洢�����С�18Kbit��36Kbit��BRAM����Դ�洢��ģ����Ż��ġ�LUTRAM����FPGA�еIJ��ұ��������ϸ���ȴ洢���Ż��ġ�Xilinx Virtex-5 FPGA�У�LUTRAM�ĵ�λ��64bit��

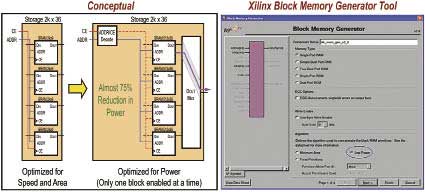

�������������У�BRAMͨ������Ҫ��һЩ�����ú��BRAM��̬�������书�ĵĽϴ֣���������Ĺ��ľ��ڵڶ�λ�������Ա���Բ�ȡһЩ�������Ż�BRAM�Ĺ��ġ����磬���Խ��ڶ���д���ڲ�����BRAM�����ڽ�С�Ĵ洢��ģ�����ʹ��LUTRAM������BRAM����BRAM�����ϴ�Ĵ洢��ģ��ʹ�á����⣬�����Գ��Խ�BRAM���ڶ������ģ�顣��һ�ּ����Ǻ������Ŵ洢��������������ռ�õ��ӳ������ʹ���ܽϴ����������书�ġ�ͼ1��������һ������ٶȺ�������Ż���2K x 36bit�洢���С�

���������ĸ�2K x 9bitģ�鲢�й�����һ�洢���У�������Ҫ��ֵʱ���ã�Enable�������ĸ�ģ�顣��һ�����Dz����ĸ�512 x 36bitģ��������2K x 36bit�������õ���λ��ַ������ѡ������ĸ�512 x 36bitģ�顣�ں�һ������£�ij��ʱ�������һ���洢���飬���Ľ��ȵ�һ�ַ�������75%��

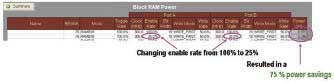

ͼ1�Ҳ���ʾ����Xilinx��˾�Ŀ�洢����������Block Memory Generator�����������������������С�Ĵ洢�����в���������ٶȻ��ʶ�������Ż���ͼ2������˾���Ӧ���е�Xilinx Power Estimator���Ƚ����ڸ�����ʹ��������N��ģ��ͬʱ������N/4ģ������ʱ�Ĺ�������������ʾ��̬���ʽ�����75%��

ͼ1 �ٶȺ�����빦���Ż��洢������(��)

�Լ�Xilinx Block Memory Generator�빦�����ѡ��(��)

Xilinx���߿ɰ���ѡ���ʺϵĴ洢�����С�����ij���������Ҫ����洢������һ���������Ҫ������300MHz��16��64 x 32bit�洢���ṹ����λ��Ϊ32K������һ���������Ҫ16��512 x 36bit �洢���ܹ� (��λ��Ϊ294K)��

��һ��16��64 x 32bit�洢���ṹ�Ĺ��ʱȽϣ�XPE������ʾ��С�洢�����нϺ���LUTRAM��ʵ�֣���������BRAM��Լ85%�Ĺ��ģ���ͼ3����������Ϊ�������BRAM�Ļ���ֻ����16��18Kλ��ģ����ʵ��16����С��64 x 32bit���Ĵ洢�����кܶ�ռ䱻�˷��ˡ����ڶ������16��18Kλ���еĹ��ʱȽϣ�XPE��ʾ��������෴��Ӧ�����ô�һЩ�Ĵ洢��������ʵ�֣�ͼ4������������£�����BRAM�Ȳ���LUTRAM���Խ�Լ28%�Ĺ��ģ�������Ϊ�������LUTRAM����Ҫ���ø����С���ȶ������Ӹ���Ļ�����

Xilinx FPGA��ʱ���ſع���

Xilinx FPGA��ʱ���ſع����ṩ��һЩ�dz�����˼����;�����磬��������BUFGMUXʱ�ӻ�������FPGA�ڵ�ij��ȫ��ʱ�ӹرգ����߶�̬ѡ�������ʱ�ӡ�������ʹ��BUFGCEʱ�ӻ��������а�ʱ�����ڣ�cycle-by-cycle�����ſأ���ASIC�����ʹ�õ�ʱ���ſؼ������ơ�����п���ͬʱʹ�������ֹ��ܡ�

��ijЩ����У�һЩģ�鲢��ʼ��ʹ�ã������ڹ���Ӱ��ȴ�ܴ�ʱ��Щ�����dz����á�����ʱ������Ϊ�������߰����ʱ�����ڵ���Ͽ�����رտ����г�ǧ��������صĴ���ʱ����

ͼ2 XPE�����Ż����н��

ͼ3 ���ÿ�RAM �� LUTRAMʵ��С�洢�����еĹ��ʹ���

ͼ4 ����LUTRAM�Ϳ�RAMʵ�ִ�洢�����еĹ��ʹ���

�ڵ�·��һ��������

PCB���ʦ����е����ʦ��ϵͳ�ܹ�ʦ�ڵ�·��һ�����Կ���ͨ����������������FPGA�Ĺ��ģ�FPGA���ں˵�ѹ�ͽ��¶��ڹ��ĵIJ�ͬ���涼�к�ǿ��Ӱ�졣

����VCCINT�ں˵�ѹ�ǰ弶�����ĵ�һ�ַ�����Դ��й©�ľ�̬�����Լ���̬���Ķ��߶�������FPGA���ں˵�ѹ����ˣ�����й©��һ�ַ������ǽ��ں˵�ѹ�����ڽӽ��ֵ��1V���ĵط��������ǹ�����Virtex-5��ѹ��Χ�ĸ߶ˣ�1.05V = +5%����

�����ִ�������ѹ�������Ի�á�1.5%�ĵ�ѹ�ȶ��ȣ������DZ��ġ�5%������ں˵�ѹ��1V�������ǽϴ�ֵ1.05V�����ɽ�й©���µľ�̬���Ľ���15%��ͬʱ��̬���Ľ���10%��

����FPGA���µ�һ�ּ����Եķ���������ɢ�ȸ��õ�PCB��ɢ������Ȼ��FPGA�����ԱֻҪ�ܹ������ĵĸı䶼��ֵ�ù����ġ��ڽ���100������ʱ��15����¶Ƚ��Ϳ��Խ�Դ��й©���µľ�̬���Ľ���20%��

ͨ�����FPGA�е��¶Ⱥ͵�ѹҲ���Խ����ġ�Virtex-5 FPGA�а�����һ����ΪSystem Monitor��ģ��ģ�飬���Լ���ⲿ���ڲ�ģ���ѹ�Լ�оƬ�ڲ��¶ȡ�System Monitor����һ��10λ��A/D�任�����ܹ���-40����+125�淶Χ���ṩȷ�ɿ��IJ��������A/D�任����Ƭ�ϴ�������������ֻ�����������������ض��17·�ⲿģ�����룬�Ӷ����ϵͳ�������ⲿ������ģ���ڰ����˿����õ���ֵ�澯��ƽ�����ҿ����ڿ����õļĴ����ڴ洢�����������˿ɷ���ؽӿڵ��û�������������

���⣬I/O���ʳ�Ϊ�ڹ��ĺ�����ƽ���������Ҫ���ǵ���һ��Ҫ���أ�ͨ����Ϊ�Ż���I/Oѡ����Խ�һ��

����Ķ�:

- ...2011/08/26 13:37��Xilinx Zynq-7000 EPPΪ���¿�����ʱ��

- ...2011/03/25 10:57����Multisim�����ж�Xilinx �ɱ�����豸���б��

- ...2009/06/02 15:08������Xilinx������CPRIЭ��ʵ�ַ���

- ...2008/08/15 15:42��Xilinx�ͳɱ���ʾ���������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������