ʱ�Ӷ���ʱ�����������

����

��ϵ�����¹��������֣���1 �����ص���������ȷ�ع���ij��ʱ��Դ�Ķ�������������ADC �Ŀ�������ϡ��ڱ��ļ���2 �����У�������϶��������ڼ���ADC �������(SNR)��֮������ʵ�ʲ���������бȽϡ�

�˲�����ʱ�Ӳ���

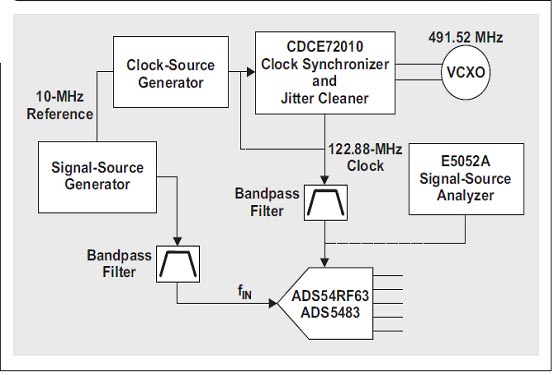

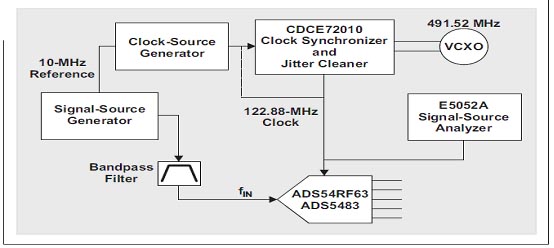

��������һ�����飬Ŀ���Ǽ����ʱ����λ��������ȡ��ADC ���SNR ��ʱ�Ӷ�����ƥ��̶ȡ���ͼ11 ��ʾ��һ��ʹ��Toyocom 491.52-MHz VCXO ��TICDCE72010���ڲ���122.88-MHz ����ʱ�ӣ�ͬʱ��������Agilent ��E5052A �����˲���λ����������в���������һ��SNR ��Ҫ�����ڲ���ʱ�Ӷ���������Ƶ�ʶ����ֲ�ͬ��TI ����ת������ADS54RF63 ��ADS5483���������������ٸ���Ҷ�任(FFT) �Ĵ�СΪ131000 �㡣

ͼ11 �˲���ʱ������Բ���װ�ýṹ

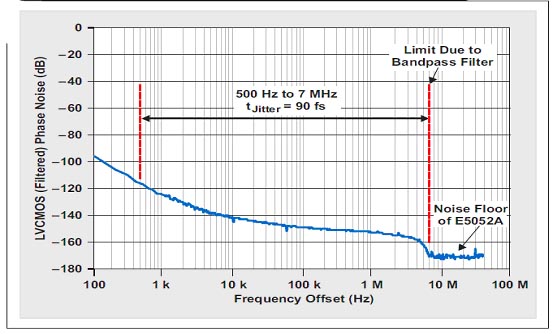

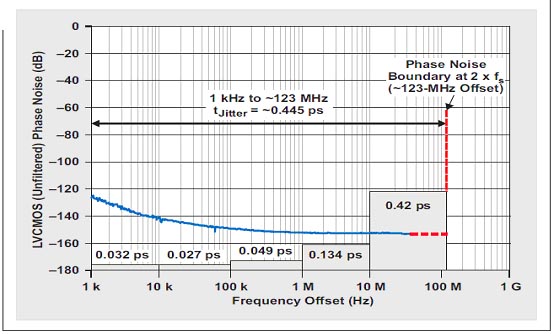

ͼ12 ��ʾ����ͼ�������˲���CDCE72010 LVCMOS ����IJ�������λ������131000 ���FFT ��С���ͻ��ִ����趨Ϊ~500 Hz�����������ɴ�ͨ�˲����趨����Ӱ������λ��������ͼ�������ɼ�����������ͼ��ʾ��ͨ�˲������Ƶ���λ����ΪE5052A ���������ޣ���Ӧ�����ڶ��������С��˲�����λ��������Ļ��ִ���~90 fs ��ʱ�Ӷ�����

ͼ12 �˲���ʱ�ӵIJ����λ����

�����������ǽ����������������ߡ�����ֱ�Ӵ�~35 fs ������ʱ��Դ������ʹ���˲������ʱ�Ӷ�����ADC ��������CDCE72010 ���ƹ��ˡ�������Ƶ���趨Ϊ10 MHz��Ԥ�ƶ�ʱ�Ӷ���SNR ��Ӱ�졣Ȼ��ͨ����������Ƶ����SNR ��ҪΪ�������Ƶ�Ƶ�ʣ�ȷ��ÿ��ADC �Ŀ����������ڲ���ʱ�Ӷ���Զ���ڹ���ADC ����������˼���Ӧ�÷dz�ȷ�������ע�⣬ʱ��Դ��������Ӧ�����ӣ���û�жൽ����ADC �Ľϴ�ֵ�����Ӷ�����ʱ���źŵ�ת���ʣ�ֱ��SNR �ȶ�����Ϊֹ��

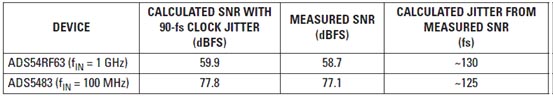

����֪��ʱ��Դ�������˲���������ⲿʱ�Ӷ���Ϊ~35 fs��������ǿ������ò�õ�SNR �����Ȼ��Ե�1 ���֣���μ��ο�����1���еķ���ʽ1��2 ��3 ��������ֵ���Ӷ�����õ�ADC ����������μ�����ķ���ʽ4����3 �о���ÿ��ADC ��õ�SNR ����Լ�����ÿ�������

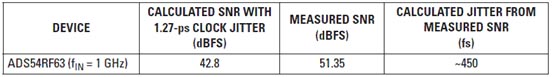

��3��õ�SNR �ͼ���ö���

����ADC ��������CDCE72010 �IJ���ʱ�Ӷ��������Լ����ADC ��SNR������ʵ�ʲ�������Աȡ�ʹ��ADC ����������ͨ�����SNR ֵ�����CDCE72010 �IJ���ʱ�Ӷ��������4 ���С�էһ����Ԥ��SNR ֵ��Щ�ӽ����ֵ�����ǣ�������ADC����ó��IJ���ʱ�Ӷ�����90 fs ���ֵ�Ա�ʱ��������һ����ͬ�ij����������൱��IJ�ƥ�䡣

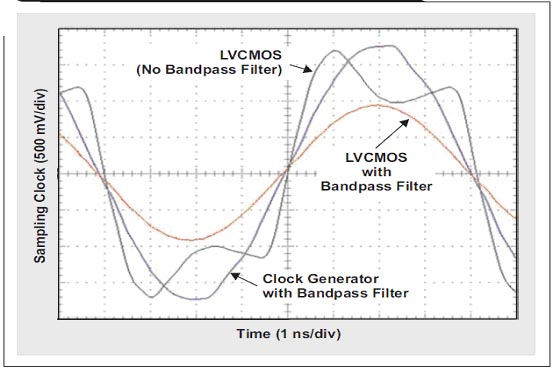

��ƥ���ԭ���ǣ�����ó��Ŀ������ǻ���ʱ��Դ�������Ŀ���ת�����ʡ�CDCE72010 ��LVCMOS ���������ʱ���źŵĸ߽�г�������������γɿ��������ء�ͼ13 ��ʾ����ͼ�����˴�ͨ�˲������罵��δ�˲�LVCMOS ���ת�����ʣ��Լ�������ת��Ϊ���Ҳ��Ĺ��̡�

ͼ13 ʱ�Ӷ����Բ���ʱ��ת�����ʵ�Ӱ��

��4 90-fs ʱ�Ӷ�����SNR ���

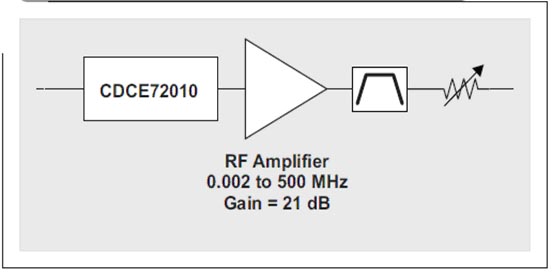

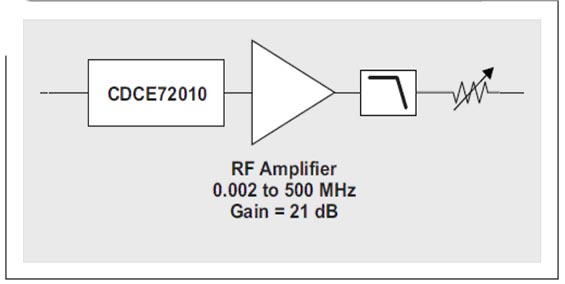

����ת�����ʵ�һ�ַ����ǣ���CDCE72010 ��LVCMOS ����ʹ�ͨ�˲���֮������һ�������൱������ĵ�����RF �Ŵ������μ�ͼ14���÷Ŵ���Ӧ�÷������˲���ǰ�棬��������Խ����ʱ���źŵ�����Ӱ��̶������˲�������������ADC ��ʱ�����������������һ������ķŴ�������21 dB �����棬��������ڴ�ͨ�˲�������������һ���ɱ�˥������ּ��ƥ���˲���LVCMOS �źŵ�ʱ���������˲��������ת�����ʡ���˥�����ɷ�ֹADC ��ʱ�����볬���ϴ�ֵ��

ͼ14 ��ͨ�˲���ǰ������RF �Ŵ���������ת������

ͨ����ʱ������ͨ·�а�װ������RF �Ŵ�������������ת�����ظ������˸�����Ƶ�ʵ�SNR �������������5 ��ʾ�����ǿ��Կ��������SNR ��Ԥ��SNR ƥ��ķdz��á�ʹ������ķ���ʽ5������õ���ʱ�Ӷ���ֵ��90-fs ʱ�Ӷ�����5 fs ���ڣ�����ͨ����λ��������Ƶ��ó���

��5 90-fs ʱ�Ӷ�����RF �Ŵ�����SNR ���

δ�˲�����ʱ������

Ϊ��ǿ���˲�����ʱ�ӵ���Ҫ�ԣ�����һ�������У����ǽ�ʱ�Ӵ�ͨ�˲�����CDCE72010 �����ȥ������ͼ15 ��ʾ�ṹ�У�����ʹ����E5052A ��λ����������������ʱ����λ���������Dz��ҵ��ǣ��÷����Ƕ���λ�����IJ������ﵽ��40-MHz �ز�Ƶ��ƫ�ƣ��������������û�и����κ���λ�������Ե������Ϣ��

ͼ15 δ�˲�����ʱ������IJ���װ�ýṹ

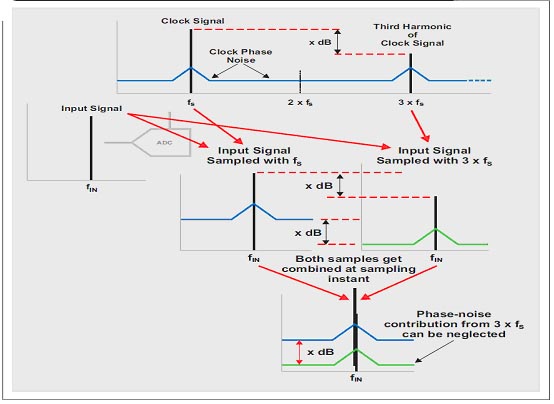

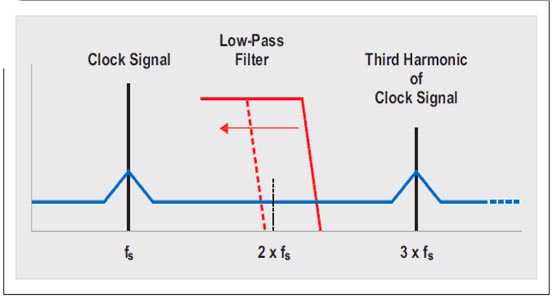

Ҫ�趨ʹ��δ�˲�ʱ��ʱ����ȷ�������ޣ����DZ�����һ�θ�ϰһ�²������ۡ�CDCE72010 ��δ�˲�ʱ�������������һ�־��п��������صķ�����������������ʱ��Ƶ�ʵĻ�Ƶ���Ҳ��߽�г��������Щг��������Ȼ�Ƶ�ͣ����������г�������Ӷ��½���

�ڲ���ʱ�䣬��Ƶ���Ҳ����߽�г���������źŻ�Ƶ����ͼ16 ��ʾ����Ϊ�˼����������ʾ��һ��г��������ˣ�����г����Χ����λ�����������źŻ�Ƶ��������г��Ҳ�γ�һ����Ƶ��������ǣ�����ʱ���źŵĵ���г����������ͣ���˸û�Ƶ��������Ҳ�����͡�

ͼ16 ����ʱ��ʱ�ӻ�Ƶ����г���������źŻ�Ƶ

���������ź������һ��ʱ�����ǿ��Կ�����һ��������쳬��~3 dB ʱ���ɵ���г�����������λ��������Ϊ��С�����ڻ�Ƶ�͵���г��֮��Ľ����Ϊ2 × fs����������λ����������2 × fs���Եõ��൱ȷ�Ľ����

�����ͼ19 ��ʾ��CDCE72010 ��δ�˲�LVCMOS �����λ������–153 dBc/Hz �����ȶ�����ʼ��~10 MHz ƫ��Ƶ�ʣ�ԭ�������LVCMOS �������������������ADS54RF63 EVM ����~1 GHz�������ڱ�ѹ������ʱ�������������������϶��ԣ�Ӧ�ÿ��Զ���λ���������Ϊ~1GHz����900-MHz ƫ��Ƶ�ʵ�3dB ʱ�½�����������~1.27 ps �IJ���ʱ�Ӷ���������fIN = 1GHz ��SNR ����~42.8 dBFS!

ͼ17 ��ͨ�˲���ǰ������RF�Ŵ���������ת������

ͼ18 ��ͬ��ͨ�˲���������λ����

ͼ19 ����(extrapolate)123-MHz ƫ��Ƶ�ʵ�δ�˲���λ����

ʵ��SNR ��������ȱ�6 ��

����Ķ�:

- ...2012/04/01 10:31��ʱ��ʱ�Ӷ���������һ��

- ...2012/03/19 10:04��ʱ��ʱ�Ӷ���������һ��

- ...2011/05/23 14:18���ź���������ʱ�Ӷ������ء���������·ʱ�Ӷ����淶����֪ʶ

- ...2009/03/11 13:16�������͵���DDR I��II �� IIIʱ�Ӷ�������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������