����FSL���ߵ��Ź��Ӽ����������ʵ��

0 ����

��ѧ�������������ӹ�ѧ�����ʵ�鳣����Ҫ���е�����ɹ��ӵ�̽������ʵ��ʵ�����ݵIJɼ���һ�㳣�õ�������һ��������̽��������һ���Ź��Ӽ���������ǰ�˵ĵ�����̽���������ռ������źţ�ÿ̽�һ�����Ӳ���һ��TTL���壬��˵��Ź��Ӽ�����������¼��TTL��������Ŀ������PC����������ͨ�Ż���ͬ����APD�Ĺ�����ʽ��Լ����Ź��Ӽ����������ھ���ʵ������ͬ��Ҫ��ͬ�Ĺ�����ʽ��������һ��ͨ�õļ���ģʽ�ܹ��������������������ڳɱ����ƣ����̶ܹ��ļ�����������Ϊû�й������г�����ɼ۸�ܸߡ���һ���棬��ҵ�Ϳ��н繺������ü����������������Լ��ľ�����������¹���Ч�ʵ��£�����������Ҫ����ν�Ź��Ӽ�����������Ե��������ӵ���ʵ���о��жԵ�������̽������������Ƶġ����������ӵ����ǶԾ����е�ȱ�ݣ������ӵ�ͽ��ʯɫ�Ľ��п��ƣ����źŶ���һ����ͨ�����������ĵ������ӽ���̽��ʵ�ֵġ��ڴ���ʵ���г��õļ��������֣��Ź��Ӽ�������ʱ��������غ�������������������ϵͳ������һ�ֿ���չ��ͨ�źͿ��Ƽܹ��ܹ����Ӳ�ͬ��ʽ�ļ������ܡ�

1 ϵͳ�ṹ���

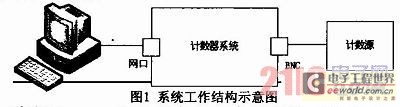

����ϵͳ�ṹʾ��ͼ��ͼ1��ʾ��ͨ��PC������̫����ʵ�������ϵͳ������ͨѶ������䣬PC��������ģʽѡ�������ͨ��������ϵͳ���ͣ���ϵͳ���ڲ�ͬģʽ�µļ���ֵ������״̬������ͨ�����ڷ��͵�PC��������PC�������ݽ��д�����ϵͳ����оƬ����Xilinx��SPARTAN 3Eϵ�е�XC3S500E��ϵͳ�Ĺ��Ӽ�������������BNC�ӿ����룬�������ӿڿ�����FPGA�������ã�ʹ���Ӽ������Բ�ͬ��ģʽ���й�����ϵͳ�Ĺ̼���д��FLASHоƬ�ڣ�SDRAM�ṩ�˴������洢�ռ䣬��������ʱװ��Microblaze���˴��롢����Ӧ�ô����Լ��洢���������ݡ�

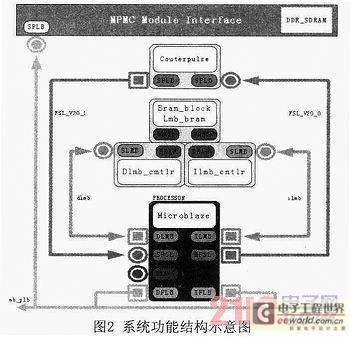

ϵͳ��FPGAΪ�������ģ�ʵ�ָ��ֹ���ģʽ���书�ܿ�ͼ��ͼ2��ʾ������ģ����Ҫ��������Microblaze�����ⲿ�洢���Ľӿ�MPMC���Լ���Ҫ���ʵ�ֵ�Counterpulse IP�ˡ���Counterpulse IP���봦��������֮�䣬������FSL���߽������ӣ�ʵ����Microbalze��Counterpu-lse�˵����ã��Լ���Counterpulse�˵�Microblaze�����ݴ��䡣

ϵͳ����ʱ����Microblaze����ͨ�����ڽ�����PC��������������������ͨ��һ·FSL���߶Թ��Ӽ���IP�˽��й���ģʽ��ѡ������á�����IP�˶��ⲿ����Դ���м����������Ľ����״̬����ͨ����һ·FSL���߷��͵�Microblaze���ˣ���Microblaze���˽���������DDRRAM�ڽ��л��壬��ͨ�����ڽ���Щ���ݽ��շ���PC������PC�����з���������

ϵͳ�����ֹ���ģʽ��ģʽһ��ʹ�ܼ�����ʹ���ź���Чʱ(�ߵ�ƽ��Ч)���Թ��Ӽ�������ļ��������źŽ��м�����ģʽ���������ڼ����������趨�ļ������ڣ��Թ��Ӽ�������ļ��������źŽ��м�����ģʽ����������ֹͣ�źŷֿ��ļ�ʱ����������ļ��������źźͼ���ֹͣ�ź�(��Ϊ��������Ч)��������ϵͳ��ƵΪ���ļ�ʱ����ʵ�ֺ���������

2 ϵͳ���ʵ��

2��1 ϵͳӲ����ͼ

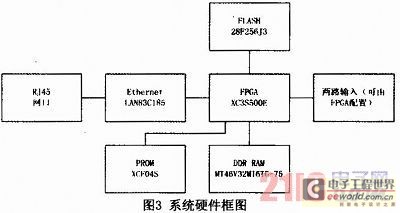

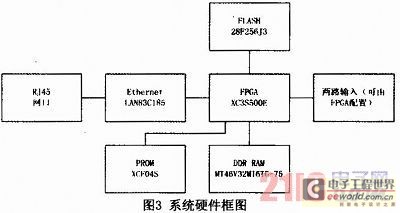

����ϵͳӲ���ṹ��ͼ3��ʾ����FPGA��64MB��DDR�洢����16MB��FLASH�洢����10M��100M��̫������(PHY)����ɡ�ϵͳ����ʱ����PC��ͨ�����ڷ������FPGA��FPGA�ڲ���Microblaze�������ü���IP�˵Ĺ���ģʽ����FPGAͨ����·BNC�ӿڶ��ⲿ����Դ���м���������������DDRRAM�ڽ��л��壬���ս���Щ����ͨ�����ڷ��͵�PC����

2��2 ��ҪԪ��������

2��2��1 FPGAоƬ��������оƬѡ��

FPGAѡ��Xilinx��˾��Spartan-3Eϵ��XC3S500E�������Ƚ���90nm���칤���������������ܶ�Ϊ50���š�Spartan3ϵ�е�FPGA��Xilinx��˾ר����Դ��������ͳɱ�����ĵ�����ƶ������ģ���֧�ֶ��ֵ�ƽ��I��O�������зḻ������Դ��XC3S500E����360kbits�Ŀ�RAM��73kbits�ķֲ�ʽRAM��10476������Ԫ��20��18×18�ij˷�����4��DCMʱ�ӹ���ģ�顣

FPGA������оƬѡ�õ���Xilinx��˾����ϵͳ�ɱ������оƬXCF04S����оƬ��ΪXC3S500E�ṩ����ʹ�á��ɱ����ҿ��ظ���̵��������ݴ�����������оƬ֧��IEEE1149��1����JTAG�߽�ɨ����Ժͱ�̡��ڱ�ϵͳ����У�XCF04S��Ҫ�����������Microblaze���˼�Ӧ�ó�����������롣

2��2��2 �洢оƬ

ϵͳʹ�õ�RAM��Micron Technology��˾��DDRSDRAM(MT46V32M16)����һƬ����Ϊ512Mbit(32Mx16)��16λ���߿��ȴ洢оƬ�������ϵ�����Microblaze���˴����Ӧ�ó�����룬�Լ��Լ������ݽ��л��塣FLASHоƬ��Intel StrataFlash parallel NORFlash���ͺ�Ϊ28F256J3���洢�ܶ�Ϊ256Mbit���ڱ�ϵͳ�����ڱ���Microblaze���˴����Ӧ�ó�����롣

3 �������ʵ��

3��1 ����EDK��FPGA����Microblaze��Ӧ�����ʵ��

ϵͳ��ƹ�����Ҫ����Xilinx��˾��Ƕ��ʽ������EDK�������������Ƕ��ʽ����ϵͳ�ļ��ɽ���������������Ӳ��ƽ̨��XPS�ͽ����������õ�SDK��

Microblaze��Xilinx��˾�Ƴ���32λ���������ˣ�֧��CoreConnect���ߵı����輯�ϡ�MicroBlaze������������150MHzʱ���£����ṩ125 D-MIPS�����ܣ����ָ�Ч�������ڱ�ϵͳ�п�����ʵ�ִ��������ܣ�ʵ�ֶԼ���IP�˵����ã��Լ�֧��Xilinx��clockgenerator��Et-hernet��IP�ˡ�ϵͳ�Լ�������ʵ�ֲ���Verilog���Խ��������ܱ�дΪIP�ˣ�����ͨ��FSL���߹���Microblaze�����ϣ���ʵ�ּ������ܡ�

2 ϵͳ���ʵ��

2��1 ϵͳӲ����ͼ����ϵͳӲ���ṹ��ͼ3��ʾ����FPGA��64MB��DDR�洢����16MB��FLASH�洢����10M��100M��̫������(PHY)����ɡ�ϵͳ����ʱ����PC��ͨ�����ڷ������FPGA��FPGA�ڲ���Microblaze�������ü���IP�˵Ĺ���ģʽ����FPGAͨ����·BNC�ӿڶ��ⲿ����Դ���м���������������DDRRAM�ڽ��л��壬���ս���Щ����ͨ�����ڷ��͵�PC����

2��2 ��ҪԪ��������

2��2��1 FPGAоƬ��������оƬѡ��

FPGAѡ��Xilinx��˾��Spartan-3Eϵ��XC3S500E�������Ƚ���90nm���칤���������������ܶ�Ϊ50���š�Spartan3ϵ�е�FPGA��Xilinx��˾ר����Դ��������ͳɱ�����ĵ�����ƶ������ģ���֧�ֶ��ֵ�ƽ��I��O�������зḻ������Դ��XC3S500E����360kbits�Ŀ�RAM��73kbits�ķֲ�ʽRAM��10476������Ԫ��20��18×18�ij˷�����4��DCMʱ�ӹ���ģ�顣

FPGA������оƬѡ�õ���Xilinx��˾����ϵͳ�ɱ������оƬXCF04S����оƬ��ΪXC3S500E�ṩ����ʹ�á��ɱ����ҿ��ظ���̵��������ݴ�����������оƬ֧��IEEE1149��1����JTAG�߽�ɨ����Ժͱ�̡��ڱ�ϵͳ����У�XCF04S��Ҫ�����������Microblaze���˼�Ӧ�ó�����������롣

2��2��2 �洢оƬ

ϵͳʹ�õ�RAM��Micron Technology��˾��DDRSDRAM(MT46V32M16)����һƬ����Ϊ512Mbit(32Mx16)��16λ���߿��ȴ洢оƬ�������ϵ�����Microblaze���˴����Ӧ�ó�����룬�Լ��Լ������ݽ��л��塣FLASHоƬ��Intel StrataFlash parallel NORFlash���ͺ�Ϊ28F256J3���洢�ܶ�Ϊ256Mbit���ڱ�ϵͳ�����ڱ���Microblaze���˴����Ӧ�ó�����롣

3 �������ʵ��

3��1 ����EDK��FPGA����Microblaze��Ӧ�����ʵ��

ϵͳ��ƹ�����Ҫ����Xilinx��˾��Ƕ��ʽ������EDK�������������Ƕ��ʽ����ϵͳ�ļ��ɽ���������������Ӳ��ƽ̨��XPS�ͽ����������õ�SDK��

Microblaze��Xilinx��˾�Ƴ���32λ���������ˣ�֧��CoreConnect���ߵı����輯�ϡ�MicroBlaze������������150MHzʱ���£����ṩ125 D-MIPS�����ܣ����ָ�Ч�������ڱ�ϵͳ�п�����ʵ�ִ��������ܣ�ʵ�ֶԼ���IP�˵����ã��Լ�֧��Xilinx��clockgenerator��Et-hernet��IP�ˡ�ϵͳ�Լ�������ʵ�ֲ���Verilog���Խ��������ܱ�дΪIP�ˣ�����ͨ��FSL���߹���Microblaze�����ϣ���ʵ�ּ������ܡ�

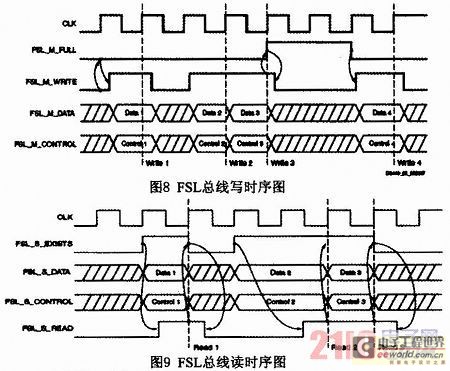

����FSL�����ǵ���ģ�����ϵͳ�в���������FSL���ߣ�ʵ��Mieroblaze������IP��֮���˫��ͨѶ������IP�����������FSL����ʱ�������ķֱ���MASTER(��)��SLAVE(��)���ֽ�ɫ����ˣ�fsloprt��v�Ĵ���Ӧ��ͬʱ������FSL���߽ӿڵĶ���дʱ��дʱ����ͼ8��ͼ9��ʾ��

3��4 ����IP�˺�FSL���ߵ���EDK�е�����ʵ��

Ϊ����ʹ��FSL���ߣ�����Ӧ����XPSͼ�ν����ж�Microblaze�������ã���Buses�н�Number of FSL Links����Ϊ1������IP Catalog�н�FSL�����뵽���������Ρ�

�ڼ���IP�˱�д���ۺ�ͨ������IP�˵��뵽XPS�����С�

��XPS�У��ֱ��Microblaze�ͼ���IP�˵�MFSL��SFSL��

����Ķ�:

- ...2012/03/31 10:53������FPGA����Ƶ���������

- ...2011/12/02 16:57������FPGAֱ��������Ƶϵͳ�����

- ...2011/11/07 15:11������FPGA�ĸ��ٴ��д���ϵͳ�������ʵ��

- ...2011/11/07 15:10������FPGA��ͨ���첽�շ������

- ...2011/11/07 15:10������FPGA��Զ�������������ϵͳ���

- ...2011/10/31 16:02������FPGA�����ݲɼ�ϵͳ���

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������