����FPGA�����ݲɼ�ϵͳ���

ժҪ�����һ�ֻ���FPGA�����Ķ�·ģ�������������ɼ��봦��ϵͳ����Ʒ�������������ϵͳ�Ľṹ��������FPGA�ڲ�Ӳ����Դ�Ļ��ֺ���������Ʒ����ȡ�����Ʒ����ⲿ��·�ṹ�ɿ����ر������ڶ�·���ϵͳ�У����ҿ��Ը�����Ҫ���ض�ϵͳ������չ�����ڼ��ϵͳ��������һ����ͨ���ԡ�

�ؼ��ʣ�FPGA��A��D�ɼ����������ɼ���Verilog HDL�������

0 ����

�ڵ������ϵͳ�У�������Ҫ�ɼ�����ģ�����źš��������źţ��������ǽ�����Ӧ�Ĵ�����һ������£����ϵͳ������ͨMCU(��51��196�ȵ�Ƭ���������DSP)�Ϳ������ϵͳ������ϵͳ��Ҫ�ɼ����ź����ر��ʱ(�ر��Ǹ����ź�����״̬��)������������ͨMCU����Դ��������������������������һ�ֻ���FPGA������ģ�������������ɼ��봦��ϵͳ������FPGA��I��O�˿ڶ࣬�ҿ������ɱ��֧�䡢�����书�ܵ��ص㣬�ܺܺõؽ���ɼ����ź�·��������⡣

1 ϵͳ���

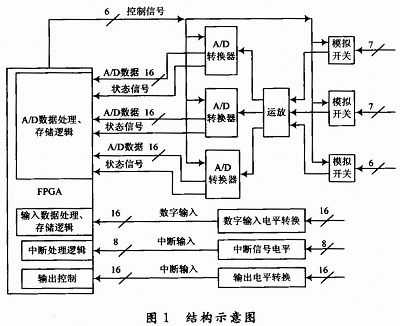

��ϵͳ�е���Χ��·�����Լ��ɿ����Ҽ���FPGA�������ص㣬ϵͳ���нϺõ���չ�ԣ��ڼ��Ϳ���ϵͳ��Ҳ����һ����ͨ���ԡ�ϵͳ��Ҫ������FPGAоƬ������·ѡ����A��D������·��ʱ�ӵ�Դ����PROM�������ص�·�ȼ����֡��ṹʾ����ͼ1��ʾ��

2 FPGAоƬ�ص��������Դ����

��ϵͳ�е�FPGA�Dz���Altera��˾��EP1C20F400����ϵ�е��ں˲���1��5 V���磬I��O�˿ڹ����ѹΪ3��3V��

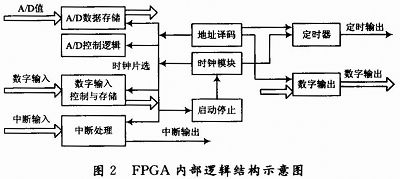

FPGA�ڲ���Դ����Ϊ�Ĵ֣���ͼ2��ʾ��

(1)FPGA���������ġ������������������ֵ����ݣ������ճ������趨�ķ��������յ������ݽ�����Ӧ�ķ����ʹ������������Դ�MCU������������ָ����з�����������ָ��Ҫ�������Ӧ����������A��D�����������ݣ������ݽ��д������洢�ȹ�����

(2)A��D���Ƶ�Ԫ����Ҫ��������ⲿA��DоƬ�Ͷ�·���ص�ѡͨʱ���Լ�ʵ�ֶ�A��D��Ҫ���̵ĺ������ƣ�����FPGAʵ��A��D�Զ��ɼ������ݴ洢��

(3)�����������Ƶ�Ԫ����������Ҫ���ӺͿ��Ƶ���������״̬���ݵIJɼ��Ϳ���������������һ������Ҫʵ������������Ŀ��ơ�����������Ĵ洢������������״̬�仯ʶ��(�ж�����)��

(4)FPGA�ӿ������Ƶ�Ԫ����FPGA�ڲ������FPGAģ�������MCU�Ľӿڵ�Ԫ���ò�����Ҫ����ͬCPU�Ľӿڣ�ʹ���ݲɼ�ϵͳ���Է������PCI��ISA�������������ӡ�

3 ģ�����ɼ��Ŀ��������

��ģ�����ɼ���Χ��·�У�A��DоƬ���õ���AD��˾��AD976A����·ģ������ͨ��AD438�Ķ�·���غ����뵽AD976AоƬ�ġ�

A��D�������ֿɷ�Ϊ���Ĵ����顢ʱ�ӷ���ģ�顢��������״̬�������ݴ洢ģ�顣

3��1 �Ĵ�����

�Ĵ������������ã���ȡA��D�Ĺ���״̬������������Ƶ�����üĴ���������ģʽѡ��Ĵ���������״̬�Ĵ�����FIFO�жϼĴ�����

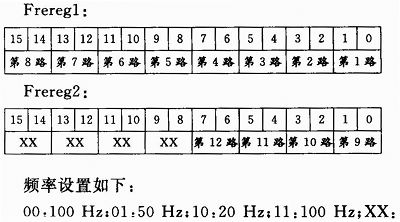

(1)����Ƶ�����üĴ���Frereg1��Frereg2(R��W)������16λ�Ĵ�������������12·A��D�IJ���Ƶ�ʣ���λ�������£�

Ƶ���������£�

�����

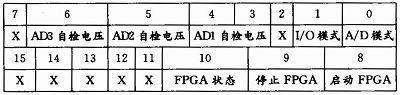

(2)����ģʽѡ��Ĵ���modereg(R��W)��176λ�Ĵ�������������A��D�Ĺ���ģʽ��������ֹͣFPGA����λ�Ķ������£�

(3)FIFO�жϼĴ���(fifo_int)(R)��16λ�Ĵ�����������¼FIFO��״̬����λ�������£�

3��2 ʱ�ӷ���ģ��

(1)��ʱ�ӷ�ƵΪ1 MHzʱ�ӣ���Ϊ״̬���Ĺ���ʱ�ӣ�

(2)����20 Hz��50 Hz��100 Hzʱ�Ӳ����Frereg��ֵ����12·A��D�����ж��źš�

3��3 ��������״̬��

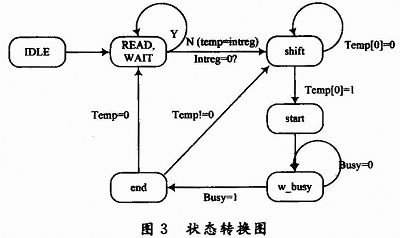

ÿ��A��D��һ����������״̬���������Զ�����A��D�����ݲɼ�����״̬ת��ͼ��ͼ3��ʾ��

IDLE������״̬��

READ��temp=intreg��������һ״̬

WAIT���ȴ��жϣ�����жϼĴ���(intreg)��Ϊ0��������һ״̬������READ��

SHIFT������temp[0]��ֵ������һ����������temp[0]=0��temp>>1��ͬʱͨ��������(counter)��1����temp[0]=1�������counter��ֵ����ͨ��ѡ���źţ�������һ״̬��

START������RC=0�źţ�������һ״̬��

W_BLISY��RC=1���ȴ�A��Dת�������źţ����������temp>>1������дFIFO�źţ�������һ״̬��

END����ЧFIFOд�źţ���temp=0�����������жϣ�coutnter=0������WAIT������counter+1������SHIFT��

3��4 ���ݴ洢ģ��

���ڴ洢A��Dת�����������ÿ·A��D��һ��FIFO��

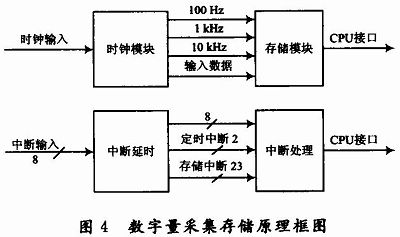

4 ���ֲɼ�ģ��

���ֲɼ�ģ����Ҫ�������������IJɼ���洢���ж��ź�״̬ʶ���ܡ���ԭ��ͼ��ͼ4��ʾ��

5 ����

���������һ�ֻ���FPGA�����Ķ�·ģ�������������ɼ��봦��ϵͳ���������Ӧ����ΧӲ����·��ϵͳ�����������ڷ�����ۺϵ��Գɹ��Ļ����ϣ���ϵͳ�ɹ�����ij�ص�Ԥ����Ŀ�Ŀ���ϵͳ�����С���������������ϵͳ�ɹ�������˶Զ�·ģ�������������IJɼ���������

����Ķ�:

- ...2012/03/31 10:53������FPGA����Ƶ���������

- ...2011/12/02 16:57������FPGAֱ��������Ƶϵͳ�����

- ...2011/11/07 15:11������FPGA�ĸ��ٴ��д���ϵͳ�������ʵ��

- ...2011/11/07 15:10������FPGA��ͨ���첽�շ������

- ...2011/11/07 15:10������FPGA��Զ�������������ϵͳ���

- ...2011/10/31 16:02������FPGA�Ľ�ͨ��ϵͳ�������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������