����FPGA�ĸ��ٴ��д���ϵͳ�������ʵ��

����0 ����

�����������缼���IJ��Ϸ�չ�����ݽ��������ݴ�������Խ��Խ���������״����������������������ʾ��㴦�����ӣ�������Ҫʵʱ����Զ�̴��䣬��Ҫ�����ȶ���Ч���źż���֧�֣��Ա��ܹ���ø��Ӿ��������շ���Ϣ�����õ�Ϊ������Ŀ����ͳ�IJ��д��䷽ʽ�������߶ࡢ�źż䴮�Ŵ��ȱ�ݣ���ͻ���������ٶ�ƿ���������д���ӵ�и��ߵĴ������ʵ�ֻ��Ҫ�������ź��ߣ������˰忪���ɱ����Ӷȣ������Ƶ��Զ���������ͨ�������㷺Ӧ�õ����ָ�������ͨ��ϵͳ����С�

����Ŀǰ�����ٴ��нӿ�ȡ���������˽ṹ�Ѿ��Ǵ�������������ܶ�û�����(��USB��PCI-Express)���ǻ��ڴ���������ʵ�ָ��ٴ���ġ�����ڲ������ߣ��������ӵ��������ܶȺ���·���Ծ��кܶ����ơ���ˣ��ܶഫ������ת���˴��д��䣬��ʼDZ�������ʾ���������ٱ��廥���ʹ洢���ڲ���������ϵͳ�漰���ļ�����Ҫ���������˴��䡢PCIE(PCI-Express)�����DDR���漼�����Լ��⼸�ּ�����FPGA���ں�Ϊһ�������Ĵ��д�����·����ʵ��������̨������֮��ĸ������ݴ�����ԣ������ʵ�ʹ���Ӧ�þ�����Ҫ����ʵ���塣

����1 ϵͳ�ṹ

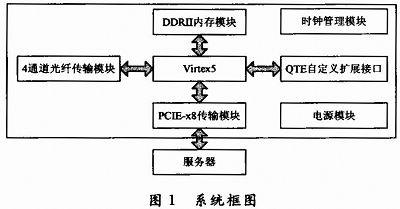

�������ٴ��д���ϵͳ��Ϊ���ݲɼ������䡢�洢�е�һ���֣��Դ�������ָ�������ϸ��Ҫ��ϵͳҪ��ɹ��źŵ�PCI-Express�ӿ��źŵ��ת��������ת��������������ݵĸ��ٴ��䡣�ź�һ��ɴ�4��25Gb��s��������˸ߵ����ݶ�Ӳ���������˺ܴ����ս��������������Ӳ���У����ٹ��ת����·��FPGA���ݴ�����·��DDR�����ݻ����·��ʱ�ӹ�����·��PCIE����ģ���·����Դģ���·���Զ�����չ�ӿڵ�·��ϵͳ��ͼ��ͼ1��ʾ��

��������Ҫ����Ҫ�����¼��㣺���ȣ����俨�е�4������ͨ����ÿͨ��Ҫ�ﵽ2 Gb��s���ϡ���Σ�PCIE�������ʲ�С��6 Gb��s��֧��DMA���䡣���У����˺�PCI-E����������ҪС��1×10-10��������������ȶ���

����ͼ1�и���ģ��Ĺ������£�Virtex5��Ϊ���俨�ĺ��ģ�����ʵ�����ݴӹ��˽ӿڵ�PCIE�ӿڵĸ���ת�������˴���ģ��������ǽ��ڲ����ݾ��������ͨ�����´��������ϵͳ���Լ��������������ݣ����������ݴ���FPGA������·DDR����ģ������ã����ǽ���������еĸ������ݣ����л��棬�Ա������ݵ������ԡ�PCI-Express����ģ������ã�������PC֮��ʵ��PCI-Express����Э�飬��PCʵ�ִ������ݴ��䣬ͬʱ���ⲿ��չ�ӿڣ�DDR���棬���˴���ģ��ʵ���ڲ��������ݵĽ�����QTE�Զ���ӿ�ģ������ã����ǽ����ⲿ������չ�����磬������չ�������ݲɼ��忨���洢Ӳ�̿���ͼ��ɼ����ȡ�ʱ�ӹ���ģ������ã��Ǹ����˴���ģ���ṩ�ο�ʱ�ӡ�ʱ��Ƶ����FPGA��ʱ�ӿ���ģ����ơ����ݹ�ģ������ܣ�����ָ����ʱ�ӡ�PCI-Express�IJο�ʱ�ӣ���ͨ��оƬ��PC��������ȡ�ġ���Դ����ģ������ã��Ǹ�����ϵͳ�ṩ���ֲ�ͬ�ĵ�ѹ��

����2 ϵͳģ�������ʵ��

����Ϊ��ʵ����Ҫ���ϵͳ���ã����õط��Ӹ�ģ���������֮������ã������ģ������ϵͳ��Э���������ϵͳ�����ݴ�����˫��ģ��ȿ��Դ������ݣ�Ҳ���Խ������ݡ�����Ҫ�ɵ�Դ����ģ�飬ʱ�ӹ���ģ�飬PCI-Express����ģ�飬DDR����ģ�飬���˴���ģ����ⲿ��չ�ӿ���ɡ����У�ʱ�ӿ���ģ���AURORA����ģ�顢Aurora����ģ����������Ƶ��ص㡣

����2��1 ʱ�ӿ���ģ��

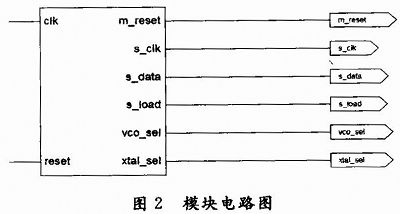

����ʱ�ӿ���ģ����Ҫ��������FPGA��Χ��ʱ��оƬICS8442����������Ҫ�ĸ�����ȡ��Ͷ����IJ��ʱ�ӡ���ģ���·��ͼ2��ʾ��������е��ź�������ɶ�ICS8442�ı�̣�ʹ���ܹ���������Ҫ��ʱ���źš�

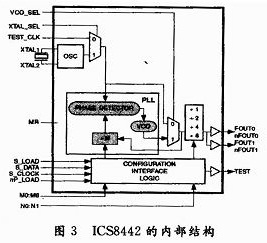

����ICS8442�����ܲ������£�����ź�Ƶ�ʷ�ΧΪ31��25��700 MHz������Ƶ�ʷ�ΧΪ10��25 MHz��VCOƵ�ʷ�ΧΪ250��700 MHz��ICS8442��LVDS����ƽ�����м��͵���λ��������������ʹ���dz��ʺ�����Ϊ��������̫����ͬ���������ṩʱ���źš�

����ICS8442���ڲ��ṹͼ3��ʾ��ICS8442�ڲ���һ��������PLL�������VCO�����Ƶ�ʷ�Χ��250��700MHz֮�䣬��Ƶϵ������M�����ģ�M��ȡֵ��Χ��10��28֮�䡣VCO�����Ƶ��Ϊ��

![]()

����ICS8442���յ���������Ҫ����һ����Ƶ��N��������������Ƶ�ʺ;�������Ƶ�ʵĹ�ϵʽΪ��

![]()

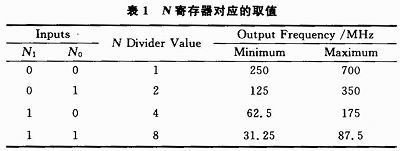

�������У�N��һ��2λ�ļĴ��������Ӧ��ȡֵ���1��ʾ��

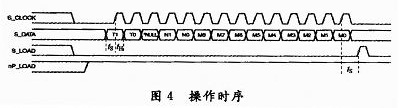

������ICS8442ʱ��оƬ�IJ�����Ҫ�ǶԼĴ���M��N��д������ICS8442֧�ֲ���д�����ʹ���д����������Ӳ����·����ƣ�������ô��е�д����ʱ��ICS8442��nP_LOAD��Ϊ�ߵ�ƽ��S_LOAD��Ϊ�͵�ƽʱ��оƬʵ�ִ��в���������ʱ����ͼ4��ʾ��

������S_LOAD��Ϊ����nP_LOAD��Ϊ��֮��������S_CLOCK�������ش��Ĵ��ڻ������У���S_LOAD���½��ش����������浽�Ĵ���M��N�С�

��������AURORA����ͨ�ŵ����ʱ��Ƶ���趨����125 MHz�����Ӳ����·����ƣ�Ӳ�������Ƶ��Ϊ20 MHz�����ѡ��MֵΪ000011001(25)��N��ֵΪ10(4)����ʱ��оƬ��ʱ�����Ƶ��Ϊ��

![]()

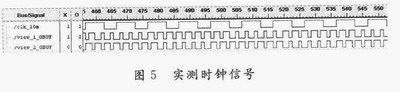

����ʱ�ӿ���ģ���ʵ��ʱ���ź���ͼ5��ʾ��

����ͼ5����Chipscope�����������ǵõ��IJ��Σ�����Chipscope�����������ǵĴ���ʱ����100 MHz�������ץȡ125 MHz��ʱ���ź�ʱ����ͼ����ʾ��ʱ���ź�ռ�ձȲ���������ʱ��оƬ������ʱ��Ƶ�ʽ��ͣ����������ʧ��

����2��2 AURORA����ģ��

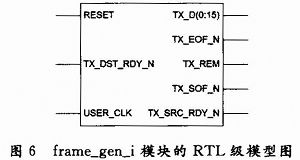

����������AURORA IP COREʱ��ͬʱ������һ������AURORAЭ�����ʾ������ˣ�Ҫʵ�ֻ���AURORAЭ��Ĺ���ͨ�ţ��ڷ��Ͷ�ֻ��Ҫ��frame_gen_iģ�齫Ҫ���͵����ݴ����Ȼ��ͨ��AURORAģ�鷢�ͳ�ȥ����˸�ģ�����ؽ�����ν���һ�������������ݽ��д��ѹ�����γ��ʺ�AURORAЭ�������֡��ͨ��AURORAЭ�鷢�͵����նˡ�ͼ6Ϊframe_gen_iģ���RTL��ģ��ͼ��

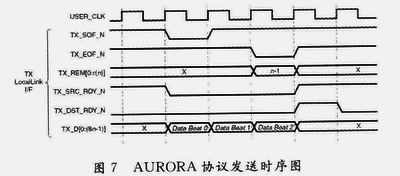

�������ǵ���һ�������������ʿ��ܻ���AURORA�����ʱ��Ƶ�ʲ�ͬ������ڷ��Ͷ˽���һ��FIFO����������������AURORAЭ��ķ���ʱ��ͼ��ͼ7��ʾ�����Կ�����TX_SOF_NΪ���ݰ�֡�Ŀ�ʼ��־��TX_EOF_NΪ���ݰ�֡�Ľ�������־��TX_REM[0��r(n)]��¼�Ϻ�Ĵ������ݵ��̣߳�TX_SRC_RDY_NΪ�ʹ���������Ч��TX_DST_RDY_NΪ�ʹ������ý������ݣ�TX_D[0��(8n-1)]�Ǵ�ģ���������ݡ�������Ϣ��AURORAЭ��ķ���ʱ����ʹ��FIFO������ʱҲӦ����ѭ������Э�顣

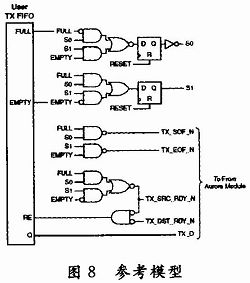

�������Ͷ˵�FIFOģ��ֱ����FIFO�ĸ�λ�źš�FIFO�ա�FIFO�����Լ�����дʱ�ӡ�ʹ�ܺ������ź��ߡ����Ӧ�ø���FIFO�ı�־λempty��full������AURORA�ķ���ʱ�ο�ģ����ͼ8��ʾ����RESET�źŵ���֮ʱ�����Ƚ�S0��Ϊ�ߵ�ƽ����S1��Ϊ�͵�ƽ��ͬʱ����FULL��EM-PTY��״̬ȷ����������S0��S1��״̬������������������ϵ�õ�TX_SOF_N��TX_EOF_N��TX_SRC_RDY_N�����źţ����Ҹ�������X_DST_RDY_N��TX_SRC_RDY_N����FIFO�Ķ�ʹ�ܡ������������Կ�����ֻ����FULLΪ1��EMPTYΪ0ʱ��FIFO�Ķ�ʹ�ܲ��ܱ���TX_SOF_NΪ���ݰ���֡ͷ��־��TX_EOF_NΪ���ݰ���֡β��־��TX_STC_RDY_NΪ��ʱ����������Ч��TX_DST_RDY_NΪ�����źţ����ݴ������ź�ȷ��FIFO�Ķ�дʱ��

������FIFOʱ�������Ҫ����������·ͼ����������������·ͼ�У���һ��D����������RESET�ź��Ǹ�λ�źţ���λ���ǽ�����������˿����㣬����S0��1����S1��0����֮ǰ�ij�����������д������RESET�źŵ���֮��S0��0��S1��1���������µĽ�����ڽϿ�ʼ�����һ�����ݶ�ʧ��֮��Ľ����������������������֮��������Ⲣ�Ѹ�����

����2��3 AURORA����ģ��

����ͬ����AURORAЭ��ģ���У�Ҫʵ�ֶ����ݵĽ��գ�ֻ����frame_checkģ���жԽ��յĴ�������ģ������Լ�����Ҫ������

����Ķ�:

- ...2012/03/31 10:53������FPGA����Ƶ���������

- ...2011/12/02 16:57������FPGAֱ��������Ƶϵͳ�����

- ...2011/11/07 15:10������FPGA��ͨ���첽�շ������

- ...2011/11/07 15:10������FPGA��Զ�������������ϵͳ���

- ...2011/10/31 16:02������FPGA�����ݲɼ�ϵͳ���

- ...2011/10/31 16:02������FPGA�Ľ�ͨ��ϵͳ�������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������