����FPGAֱ��������Ƶϵͳ�����

ժҪ ���һ������ͨ��ϵͳ�����š��������Լ����ྶ���������ȱ�㣬�����һ�ֻ���FPGA��ֱ��������Ƶϵͳ��ơ�����Ʋ���63λ��pn����Ϊ��Ƶ���Ƶ������У��ڷ��Ͷˣ�����Ϣ�������Ƶ���ƣ��ڽ��նˣ����յ�����Ƶ�����źŽ��н�������ǿ��ϵͳ�Ŀ������ԺͿɿ��ԡ�ͬʱ��Altera��˾��Quartus�������У�ʹ��Ӳ����������VHDL��ԭ��ͼ���ϵķ��������˵�·�����ʵ�֡�ͨ���ѵ�·�²õ�Altera��˾��CycloneIII��EP3C10E144C8NоƬ�е��ԣ���֤����Ƶϵͳ�Ŀ����ԡ�

�ؼ��� ��Ƶ��pn�룻FPGA

������Ƶͨ��ϵͳ���п������Ժá����ྶ˥������ǿ���ɸ߾��Ȳ�������ַ���õ��������ԣ��������õ���Ѹ�ٷ�չ�㷺Ӧ�á�

1 ֱ��ϵͳ����ԭ��

ֱ����Ƶͨ�ž����ڷ�������ø�������Ƶ����ȥ��չ��Ϣ���ݵ�Ƶ�ף�����α����ƺ��ز��������������̡���һ�㳣����խ��ͨ�ŷ�ʽ��ͬ����Ҫ��������Ϣ���ݾ���չƵ���Ժ��Ϊ�����źţ��پ�����ش����ָ���խ���źź�������Ϣ���ݣ�����������ź���ش�����α���������������ص㡣

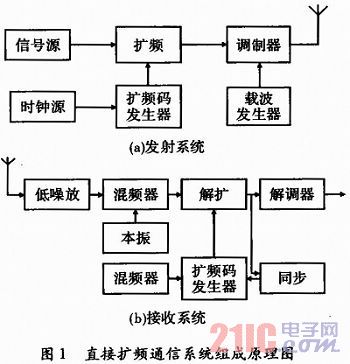

ֱ����Ƶͨ��ϵͳ���ԭ����ͼ1��ʾ���ڷ����������Ϣ�Ⱦ���Ϣ���Ƴ�Ϊ�����źţ�Ȼ������Ƶ�뷢������������Ƶ�����е��������ź���չ���źŵ�Ƶ�ס�չ������ź��ٵ��Ƶ���Ƶ���ͳ�ȥ���ڽ��ն˽��յ��Ŀ�����Ƶ�źţ���Ƶ����Ƶ��Ȼ���ɱ��ز������뷢����ͬ����Ƶ������ȥ��ؽ������پ���Ϣ������ָ���ԭʼ��Ϣ�����

2 ϵͳ���巽��

�ڷ���ϵͳ�У����Ȳ���8λ�Ĵ�����Ϣ��data_in��Ȼ��������pn�뷢��������Ƶα�����н���ģ2�ӣ�����źŵ�Ƶ����չ���õ���Ƶ�ź�data_kuo���ڽ��ն˾���pn��ͬ���������Ƶ�����ź��뱾��ͬ����Ƶ���н���������㣬�õ������ź�data_jie���Ƚ�data_ kuo��data_jie����ͼ���Ӷ���֤ϵͳ��Ƶ������Ч��������ԡ�

3 ϵͳģ�黯���

3. 1 ��Ϣ������ģ��IJ���

��ģ�鹦��������8λ��λ�Ĵ�������ʱ���źŵĿ�������λ���8λ��Ϣ�롣clrΪװ���źţ���clr=0ʱ���Ӳ��뿪�ز��ж���8λ��Ϣ�룬װ�뵽�ڲ�8λ�Ĵ����У���clr=1ʱ���������8λ��Ϣ����ʱ���źŵĿ�����ʵ�ִ�����λ�����

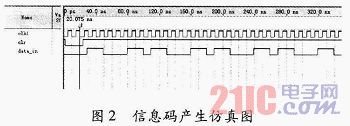

��������ͼ2��ʾ����Ƶǰ��������ϢΪ11000110B��

3. 2 pn�뷢���������ֻ����

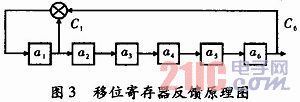

��ǰ��������ϵͳ��pn�뷢��������m���з�������n��������λ�Ĵ����ķ�����������������ʽf(x)=c0+c1x+c2x2+…+cnxn��ʾ��m���з�����ѡ��6����λ�Ĵ�������n=6������õ��ķ���ϵ��Ϊ103��������Ӧ����������ʽΪf(x)=x6+x+1���ɵ�1���͵�6�����ط�������λ�Ĵ�������ԭ��ͼ��ͼ3��ʾ��

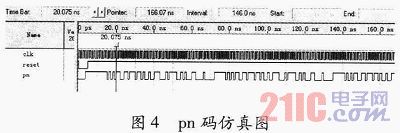

6��m���з������ɲ�������Ϊ63��pn�����У��Ĵ�����ʼ������Ϊȫ�㣬�������Ҳ��Ϊȫ�㣬���������pn�뷢������������״̬�����Ҫʹpn�뷢����������������������Ԥ�ڵ�pn���У����뱣֤����ʼʱ�Ĵ�����������һ��Ϊ1��63λpn�����ͼ��ͼ4��ʾ��

3��3 ��Ƶ���Ƽ����ģ���ۺϷ���

��ʵ��Ӧ���У�Ϊ�ﵽ���ݷ�����Ƶ��Ŀ�ģ�ͨ��������������һ��Ƶ���������������ź���ˣ�������Ƶ���о��б����ݱ���խ�ö��ʱ�����Ӷ�ʹ��Ƶ���о��б��������иߵö��Ƶ����

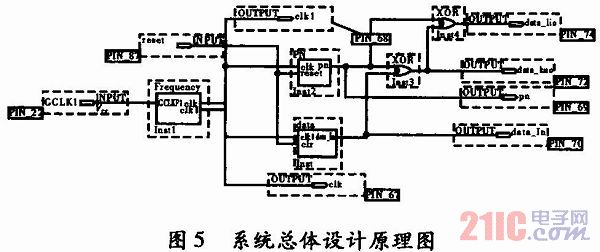

ϵͳ������Ƶ�ԭ��ͼ��ͼ5��ʾ���ڱ���ϵͳ������У�����˺ͽ��ն˶����������ݷ���ͬ������ģʽ��Ҳ����˵��pn�����������ݷ��ŵ�ƽ�仯�ض��룬��ÿ�������ظ�һ�Σ��ڽ��նˣ�Ҳ��ͨ��һ�����ݷ���ʱ����ͬ��һ��pn�����У��ڲ���һ��pn�����е�ͬʱ��ʵ�������ݷ��ŵ�ͬ�������������������̲���ʱ�䣬���һ�����ʡȥһ��խ������ͨ������������ɵ�ʱ��ͬ��ϵͳ������ϵͳ��ơ�

�ڱ�������У�һ�����ݷ�����ͬ��һ��63λ��pn�����У�pn����pn�뷢����ģ�������63λm���У�data_in����Ϣ������ģ������Ĵ�����Ϣ�룬�ڴ�ͼ��Ϊ11000110���ݷ��ţ�data_kuo�DZ���Ƶģ���������ڷ��Ͷˣ���Ƶ�Ľ��ʵ�����Ƕ����߽���ʱ����ˣ�������ģ���ͣ�����ʵ����һ�����ݷ���ͬ��һ��63λ��pn�����У�����˷���ͬ������ģʽ��Ȼ��������pn�뷢������α�����н���ģ2�ӣ�����źŵ�Ƶ����չ���ڽ��նˣ�data_kuo�뱾��ͬ��pn��ģ���ͺ��źŵĽ�������������ź�Ϊdata_jie��

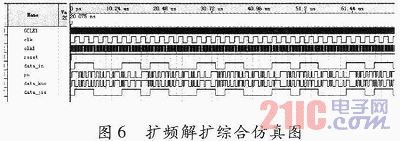

��Ƶ�����ۺϷ���ͼ��ͼ6��ʾ������data_inΪ��������Ķ�������11000110����Ϣ�������ʱ���ź�Ϊclk��pn�뷢������ʱ���ź�Ϊelk1��pn�Dz�����63λpn�����У�data_kuoΪ��Ƶ��������У�data_jie��������źţ�ʵ�����źŵĽ�����

4 ϵͳ��FPGAʵ��

ϵͳѡ��Ahera��˾������CycloneIIIϵ�е�FPGA(EP3C10E144C8N)��Ahera��˾�����CycloneIII FPGA����һ��FPGA�Ĺ��ĵ�75��������144��������ɣ���ЩI��O����֧��6�ֵ����źű���8�ֲ�ֱ�������10 kbit����Ԫ(LE)��23�������źŴ���(DSP)�˷������洢����400 kbit��CycloneIIIϵ�б�ǰһ����Ʒÿ����Ԫ�ɱ�����20����ʹ�����Ա�ܹ�������ڳɱ����е�Ӧ����ʹ��FPGA��

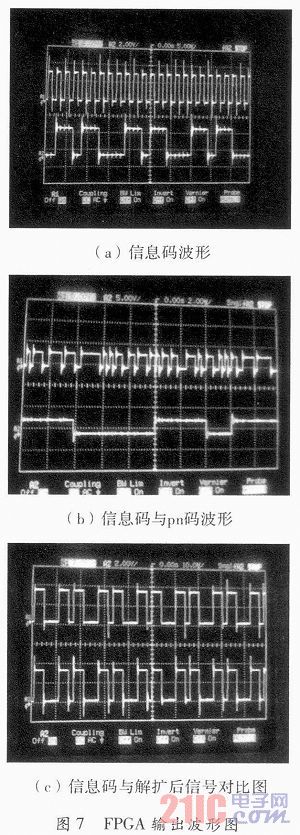

��VHDLԴ����ͨ��JTAG�����ص�FPGA�У����ú�FPGA���ź������뽫FPGA��������������FPGA��������ŷֱ���ʾ���������������ӣ��۲�ϵͳ������ͼ7��ʾ����ͼ�п��Կ���FPGA�������ͼ�����ͼ�Ǻϣ��Ӷ���֤��ϵͳVHDL�������ȷ��������ԡ����⣬����ϵͳʱ��Ƶ�ʽϸߣ����δ��ڽ�Ϊ��Ϊ���ԵĹ�������

5 ������

�����һ�ֻ���FPGA��ֱ��������Ƶϵͳ����ƣ�ּ��ʹ����ͨ��ϵͳ���н�ǿ�Ŀ������ԺͿɿ��ԡ���Altera��˾��Quartus II����ƽ̨�ϣ�������Ӳ����������VHDL��ԭ��ͼ���ϵķ��������˵�·�����ʵ�֣������������ص�FPGA�У�����ʾ�����۲�������Σ�ͨ��������ν���۲챾ϵͳ����Ƶ�������ܡ�

����Ķ�:

- ...2012/03/31 10:53������FPGA����Ƶ���������

- ...2011/11/07 15:11������FPGA�ĸ��ٴ��д���ϵͳ�������ʵ��

- ...2011/11/07 15:10������FPGA��ͨ���첽�շ������

- ...2011/11/07 15:10������FPGA��Զ�������������ϵͳ���

- ...2011/10/31 16:02������FPGA�����ݲɼ�ϵͳ���

- ...2011/10/31 16:02������FPGA�Ľ�ͨ��ϵͳ�������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������