����FPGA��ͨ���첽�շ������

ժҪ������Verilog HDL������ΪӲ�����ܵ�����������ģ�黯��Ʒ����ֱ������ͨ���첽�շ���(UART)�ķ���ģ�顢����ģ��Ͳ����ʷ�������������ֳ��ɱ��������(FPGA)���ص㣬ʵ����һ������ֲ��UARTģ�顣����Ʋ���ʵ���˴����첽ͨ�ŵ���Ҫ���ܣ����ҵ�·�������ȶ����ɿ������Խ�������Ƕ�뵽����ͨ��ϵͳ�С�

�ؼ��ʣ�ͨ���첽�շ������ֳ��ɱ�������У�Verilog HDL������ͨ��

����ͨ��Ҫ��Ĵ������٣��ɿ��Ըߣ��������Զ�����㷺Ӧ���ڼ��������������ݽ�����ͨ������ͨ���첽�շ���(UART)��ʵ�ִ���ͨ�ŵĹ��ܡ���ʵ��Ӧ���У�����ֻ��ҪUART�ļ�����Ҫ���ܣ�ר�õĽӿ�оƬ�������Դ�˷Ѻͳɱ���ߡ�����FPGA��CPLD�ķ��ٷ�չ�������ִ���������еĹ㷺Ӧ�ã�FPGA��CPLD����ǿ��������Ͷ��С�����ڶ̡��ɷ�����̡������Ժõ��ص�ҲԽ��Խ���ԡ���˿��Գ����������Դ����оƬ�ϼ���UART����ģ�飬�Ӷ����˵�·����С�����������˿ɿ��ԣ��������ʱ������Ը������ڸ��̡����ڴ˱��������һ�ֲ���FPGAʵ��UART���ܵķ�����������Ч�ؽ���������⡣

1 UART�Ĺ���ԭ��

UART(Universal Asynchronous Receiver Transmitter��ͨ���첽�շ���)�ǹ㷺ʹ�õ��첽�������ݴ���Э�顣�ڴ���ͨ���У��������ֽ�Ϊ��λ���ֽ�֡���д��͡����Ͷ˺ͽ��ն˱��밴����ͬ���ֽ�֡��ʽ�Ͳ����ʽ���ͨ�š�UART�������������һ֡�������ݰ���1λ��ʼλ(�͵�ƽ)��5��8λ����λ��1λУ��λ(��ѡ)��ֹͣλ(��Ϊ1��1��5��2λ)����ʼλ���ֽ�֡�Ŀ�ʼ��ʹ�����ߴ�����0״̬����������ն˱�����ʼ��������֡����ʹ���ͺͽ����豸ʵ��ͬ���Ĺ��ܡ�ֹͣλ���ֽ�֡����ֹ��ʹ�����ߴ�����1״̬����������ն˱�������֡������ϡ������ʲ��ñ�����9 600 b��s�������ڴ���ʱ����λ��ǰ����λ�ں��ն˼�Ⲣȷ����ʼλ��������λ��ֹͣ

λ������Ϻ���CPU�����ж��źţ�ͬʱ�����ݷ��͵��������8λ���������ϣ���������ʱ������CPU���ò����ʣ�Ȼ��8λ�������ݼ�����ʼλ��ֹͣλ�������衣ֹͣλ������Ϻ���CPU�����ж��źš������ݷ��ͺͽ��չ����У�CPU����ͨ�������ź�����ȡUART�Ĺ���״̬���Ա����ʵʱ������

2 UART��ģ�黯���

2��1 ϵͳ����ṹ

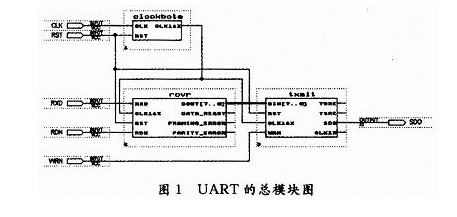

�ڴ��ģ��·������У��㷺���ò�λ����ṹ������Ʒ���������һ��������Ӳ����������ϵͳ����ʼ������Ϊ���ɸ��ɲ�����ģ�飬���Ƴ���Ӧ��ģ�Ͳ����з�����֤���Ϻ���ϵͳ���Ͻ�����ϡ�������������Ч�ʵ�ͬʱ������������������Ŀǰ��������ϵͳʵ�ֵ���Ҫ�ֶΣ�Ҳ�DZ������˼��Ļ���������ϵͳ���ܽ��л��֣�UART��Ҫ�ɲ����ʷ�����������ģ��ͷ���ģ��������ɡ���Maxp-lus����滷���£��ɸ�����ģ������ۺϵ�ϵͳ��ģ����ͼ1��ʾ������ֱ����۷���ģ�顢����ģ��Ͳ����ʷ�����ģ��ľ���ʵ�ֹ��̡�

2��2 ����ģ��

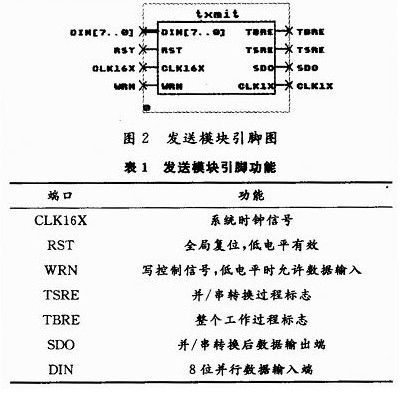

2��2��1 ����ģ�鼰�书��

����ģ����Ҫʵ�ֶԲ������ݵĻ��桢����ת�������Ѵ������ݰ��ռȶ�����֡��ʽ�������������ģ���������ͼ2��ʾ�������Ź��ܼ���1��

��CPU�����Ĵ����͵IJ������ݣ�����д�뷢�ͻ�����TBR[7����0]�����ͻ������������ݴ�����ʱ�������Զ�װ����λ�Ĵ���TSR[7����0]���Զ���ɴ������ݵķ��͡����ȴ���һλ��ʼλ0��Ȼ�����֡�ṹ�ж�������ݳ��ȣ��ֱ����Ƴ�TSR[7����0]�е����ݣ����ݵĵ�λ��ǰ����λ�ں�û�����ݷ��͵�ʱ��SDO�ܽű��ָߵ�ƽ��

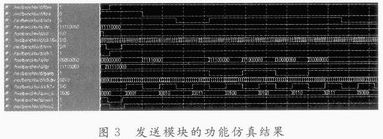

2��2��2 ����ģ�鹦�ܷ���

���������ܷ�������ͼ3��ʾ����������11110000������DIN[7����0]�������룬��WRNΪ0ʱ���������ͳ���������ʼ������ʹ�������������������浽���ͻ�����TBR[7����0]����ͨ��������λ�Ĵ���TSR[7����0]��λ��λ���ʹ����������������������SDO�������ݷ�������������ź�TBRE��TSRE��Ϊ��־�źš���һ֡�����ɷ��ͻ�����TBR[7����0]�͵�������λ�Ĵ���TSR[7����0]ʱ��TBRE�ź�Ϊ1���ɷ������ݻ���������������λ�Ĵ�����Ҫ���ź�TSRE���ơ���TSREΪ1ʱ����ʾ������λ�Ĵ���TSR[7����0]���з�����ϣ�Ϊ0ʱ��ʾ��û

�з�����һ֡���ݡ��ɷ�������֤�˷���ģ�����ȷ�ԡ�

2��3 ����ģ��

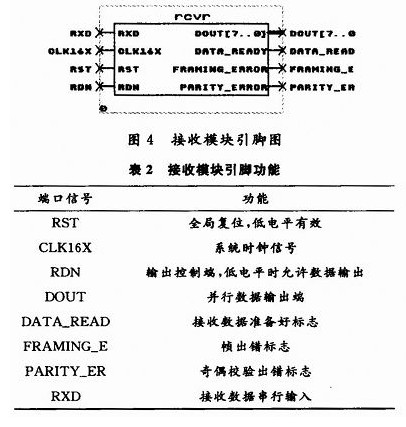

2��3��1 ����ģ�鼰�书��

����ģ��������ǰ��յ��Ĵ�������ת���ɲ������ݽ�����������ж��յ��������Ƿ��д�������ģ���������ͼ4��ʾ�������Ź��ܼ���2��

��������������������״̬�����ϼ��Ӵ���������RXD�ˣ�������ֵ͵�ƽ������������ʼλ����·����ȷ�ϣ�һ��ȷ��Ϊ���յ���ȷ����ʼλ�����Բ�������Ϊ����ʱ�ӣ���ÿ������λ���м�λ�ò���һ�Σ����Ѳ���������Ϣ����λ��ʽ���˽�����λ�Ĵ���RSR�����յ�һ֡����λ�Ѵ�������ת���ɲ������ݣ���������żУ�顢ֹͣλ����ֹ̬�ļ�顣������Ϻ�DAT_READ��1��

2��3��2 ����ģ�鹦�ܷ���

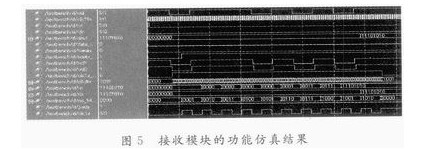

����ģ�鹦�ܷ�������ͼ5��ʾ����������11101010������RXD�������룬��������Ҫ����ʼλ����RDN�ź�Ϊ0�����£��������ճ���������ʼ���������ݴ�RXD[7����0]�������룬�ɽ�����λ�Ĵ���RSR[7����0]��λ��λ���գ����ڽ������ʱ�������ջ���Ĵ���RBR[7����0]���Ϻ���ջ���Ĵ���RBR[7����0]�����յ����ݴ�����DOUT[7����0]���������������ͬʱ���һ���������������ź�DATA _RE��־���ݽ�����ϡ�

2��4 �����ʷ�����ģ��

2��4��1 �����ʷ�����ģ�鼰�书��

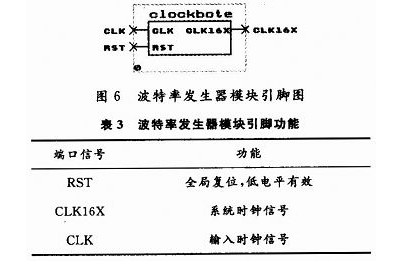

�����ʷ�����ģ����Ҫ���ڲ�������ģ��ͷ���ģ���ʱ��Ƶ�ʣ���ʵ�ʾ���һ����Ƶ�������Ը��ݸ�����ϵͳʱ��Ƶ�ʺ�Ҫ��IJ�������������ʷ�Ƶ���ӣ���Ϊ��Ƶ���ķ�Ƶ���������ʷ�����������ʱ��Ƶ��CLK16X���Dz�����ʱ��Ƶ��CLK�����Dz�����ʱ��Ƶ��CLK��16���������ʷ�����ģ���������ͼ6��ʾ���书�����3��ʾ��

2��4��2 �����ʷ��������ܷ���

UART�ڷ��ͻ��������ʱ��ʹ�õ�ʱ���ź�Ƶ��f�Dz�����(b=9 600 b��s)��16�������ⲿϵͳʱ�ӽ���16��Ƶ�õ���UARTÿ16������ʱ�ӷ��ͻ����һ��������λ������в��õľ���Ƶ��c=25 MHz����ô�����ʷ����������ʱ���ź�����Ϊ��

![]()

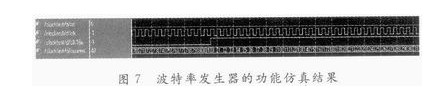

�����ʷ������Ĺ��ܷ�����ͼ7��ʾ��

������þ���Ϊ25 MHz���ɹ�ʽ�ɵó�������εİ������ӦΪk��2����81��������ʱ�����ڣ���������֤�˲����ʷ�����ģ�����ȷ�ԡ�

3 ����

UlART�ǹ㷺ʹ�õĴ�������ͨ�ŵ�·������Ҫ��Ĵ������٣��ɿ��Ըߣ��������Զ������ϵͳ�以���������첽����ͨ�Žӿڷ�ʽ��������Verilog HDL���ԣ��������״̬������Ʒ���ʵ����UART�Ĺ��ܣ�������Ĺ��ܼ��ɵ�FPGA�ϣ�ʹ������ƽ��ա�С�ɣ�ʵ�ֵ�UART�����ȶ����ɿ���ͬʱ����������״̬���ķ������нṹģʽֱ�ۼ�������̶̣������η��������ۺϣ��ɿ��Ըߵ��ŵ㣬�ؽ���EDA�����з�����Ҫ���á�

����Ķ�:

- ...2012/03/31 10:53������FPGA����Ƶ���������

- ...2011/12/02 16:57������FPGAֱ��������Ƶϵͳ�����

- ...2011/11/07 15:11������FPGA�ĸ��ٴ��д���ϵͳ�������ʵ��

- ...2011/11/07 15:10������FPGA��Զ�������������ϵͳ���

- ...2011/10/31 16:02������FPGA�����ݲɼ�ϵͳ���

- ...2011/10/31 16:02������FPGA�Ľ�ͨ��ϵͳ�������

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������