����FPGA�Ľ�ͨ��ϵͳ�������

ժҪ��Ϊ�˶Խ�ͨ��ϵͳ���о�ȷ���ƣ�����FPGAʵ��壬��Quartus�����������£��ֱ�ʵ�����巢��ģ�顢״̬��ʱģ�顢��ͨ����ʾģ�顢ʱ����ʾģ�飬���з���ʵ���Ӳ�����أ���õIJ��Խ���������Ҫ�����ڲ�����EDA������ʹ����ϵͳ��Ƶ�Ч��������ߡ�

�ؼ��ʣ�FPGA��Quartus��ͨ�ƣ�����ϵͳ���

Ŀǰ��ͨ�ƹ㷺Ӧ���ڵ�·��ͨ�����С��������һ��ʮ��·�ڽ�ͨ�ƿ��Ƶ�·��Ҫ�������ϱ������ɵ��ĺ졢�̡��ƽ�ͨ�ư�Ҫ��ѭ���仯�����Ե���ʱ��ʽָʾ�ɵ�ͨ�л��ֹ��ά��ʱ�䡣��Quartus��������������ơ����棬����FPGAʵ�����ʵ������Ƶ�·�Ĺ��ܡ�

1 ϵͳ����

1��1 ���˼��

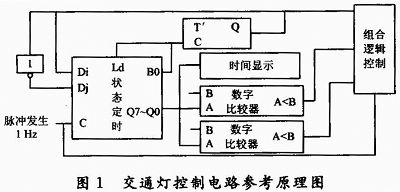

����FPGA�Ľ�ͨ��ϵͳ������ư���4��ģ�飬�ֱ�Ϊ���巢����״̬��ʱ����ͨ����˸�Ŀ��ơ���˸ʱ��Ŀ��ƣ�����ԭ����ͼ1��ʾ��

1��2 ���幤�����

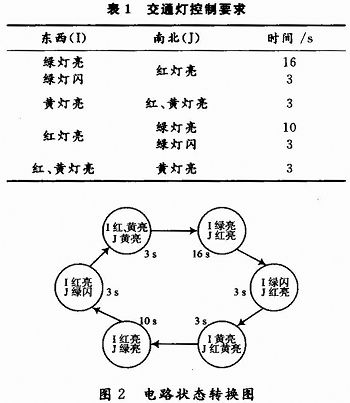

��ͨ�ƿ���Ҫ�����1��ʾ��

����ƵĽ�ͨ�ƿ��Ʒ�Ϊ6��״̬�����ڸ�״̬����ʱ�䲻ͬ�����Ե�·�ĺ��Ŀ��Ʋ�����״̬���Ͷ�ʱ����״̬���ڶ�ʱ��������������ѭ����״̬�����6������һ���Ĺ��ɱ仯���仯�����ͼ2��ʾ��

ϵͳ������FPGA�����徧����Ƶ��·ʵ�֡�״̬��ʱ��74190����ʮ���Ƽ�������T’������ʵ�֣�ֻҪ������������ת�źŵ�λ���Ϳ���ʹ��·�ڶ���(I)���ϱ�(J)��������״̬�䷭ת���졢�ơ��̵Ƶ���˸��7485���ֱȽ�������������ƣ�����7485���ֱȽ������ڱȽϼ�������ǰ����״̬������Ҫ��״̬ȫ��ʱ�䣬��������Ӧ�ı仯�������������AHDL�ļ���д��ֵ��ʵ�֡�ʱ����ʾ��AHDL�ļ���д��ֵ��ʵ�֣�������ȷ�������߶������·���ܵõ���ȷ��ʱ����ʾ��

1��3 �����ܵ����

������·���Է�Ϊ4�֣��������巢����״̬��ʱ��ʱ����ʾ�����ֱȽ�һ��������ơ�

1��3��1 ���巢��

���巢����Ϊ����ϵͳ�ṩ������������˷����FPGAʵ����PIN55���ţ������ʵ����ϲ���Ƶ��Ϊ10 MHz���������壬��7Ƭ7490��ÿһ��������10��Ƶ��·��ʹƵ�ʴ�10 MHz����Ϊ1Hz��

1��3��2 ״̬��ʱ

״̬��ʱ����Ԥ��BCD���ֵ��74190����ʵ�֣����ɼ�������������ԭ���ǣ���λ��������ȫ0״̬��Ϊ�ϴ���ֵ״̬ʱ��ʹ��λ��������1��������ʽ��Ϊ�첽��ͬ�����֣����IJ�ȡ�����첽������ʽ������λ����������źſ��Ƹ�λ�������ļ�����������ˡ��ɸ��ݼ�������ʱ�Ӵ�����ʽ���ڵ�λ������״̬���ȫ“0”��Ϊ�ϴ���ֵ��˲�䣬Ϊ��λ�������ṩ��Ч�ļ���������ء����������ǽ���Ƭλ������ź�RCON�˿ڽӵ���Ƭλ�ļ�������CLK��ʵ����λBCD�����������ת�ͽ�λ��ʹϵͳ��ʾ����������22��16֮��ѭ����

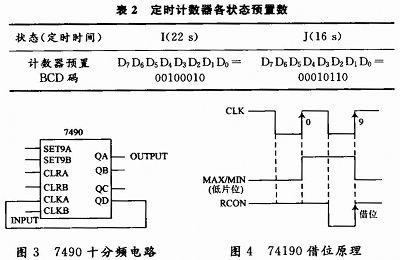

74190����˵����

(1)GNΪ������ʹ�ܿ��ƶˣ��͵�ƽ��Ч����GNΪ�ߵ�ƽʱ����ֹ������

(2)DNUPΪ������ʽ���ƣ��Ӹߵ�ƽΪ���������ӵ͵�ƽΪ�Ӽ�����

(3)LDNΪ�첽Ԥ�������ơ���LDNΪ�͵�ƽʱ��������״̬QD��QC��QB��QA�ֱ����D��C��B��A��

(4)������λ���ɸ�����˳��ΪQD��QC��QB��QA��QDΪ�ϸ�λMSB��QAΪ�ϵ�λLSB��

(5)��������CLK����������

(6)�����������QDQCQBQAΪʮ���ƼӼ����Ľϴ�״̬��“1001”��Ϊ�������Ľ�С״̬��ȫ“0”ʱ����ֵ״̬��ָʾMAX��MIN���Ϊ�ߵ�ƽ��

(7)����ֵ״̬��ָʾMAX��MINΪ�ߵ�ƽ��CLKΪ�͵�ƽʱ������ź�RCONΪ�͵�ƽ����RCON���������ͬ����

ϵͳ��������Ϊ1 Hzʱ�����2��ʾ����I״̬(��������״̬)�Ķ�ʱʱ��Ϊ22 s��������Ӧ����Ԥ��22��BCD�룻ͬ����J״̬(�ϱ�����״̬)֮ǰӦ��Ԥ��16��BCD�롣

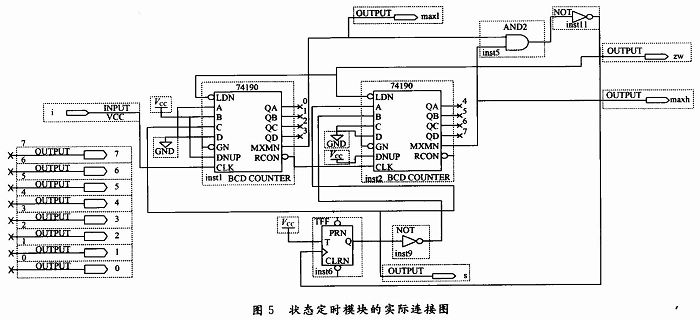

״̬��ʱ��·����Ƭ74190�������ɣ�����22��16�Է�ת�ĵ�·����Ҫ����ĺ������������������ת�ͽ�λ������74190оƬ���ص㣬�ɷ�����ʵ��ԭ����ͼ4��ʾ��ͨ������ź�RCON��������ʵ�ֽ�λ��ʹ�������ܹ���20��19����λ��ʮλ��λ��˳�����ɡ�

�����ͷ�ת֮�����Ⱥ��ϵ��������������ת�����3��ʾ����������BCD���λ�ص㣬��֪����D7D6D3D0λ��Ϊ1��D1λ��Ϊ0����D5D4D2λ��ͬ����ͼ5��D5D4D2λ��״̬��ƽS�����ƣ���ΪI״̬ʱ����������Ԥ�õ���ΪD5=0��D4=D2=1����ΪJ״̬ʱ����������Ԥ�õ���ΪD5=1��D4=D2=0������74190�Ĺ��ܣ���2Ƭ74190��MAX��MIN������ͨ������ţ��ֱ����ڸ�λ�͵�λ��LDN�����ˣ�ͨ��������֪������������01����00ʱ�ߵ�λ��MAX��MIN��Ϊ�ߵ�ƽ������������Ժ�Ϊ�͵�ƽ��74190��������������ֵ��״̬S��������S����LDN���źž�

��һ��T’�����������ģ���LDN�ź�ÿ����һ�Σ�S��ת1�Σ��Ӷ�����16��22״̬��������ṹ���ɷֱ�����16��22��ʹ��ʵ���Է�ת��

ͼ5Ϊ״̬��ʱģ���ʵ������ͼ��

1��3��3 ʱ����ʾ

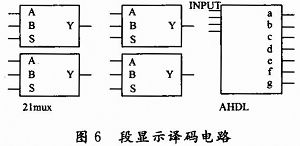

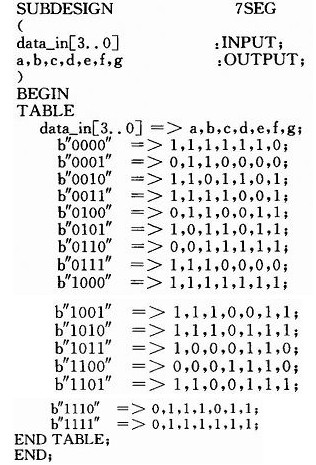

ʱ����ʾҪ�õ�7����ʾ�����·����������λBCD�룬���ö�ѡһ����ѡ������ѡ���S��һ��Ƶ�ʺܸߵķ���(��1 kHz)�����ݱȽ����������1 Hz������ΪAHDLģ������룬������ȷ��ʾʱ�䡣

![]()

Ϊ��ȷ��ʾʱ�䣬��AHDL�ļ��Ա�������ֵ�����£�

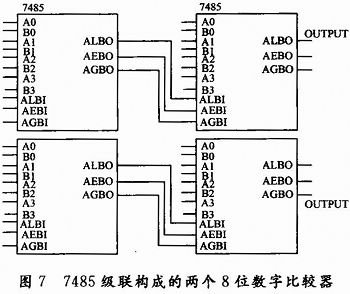

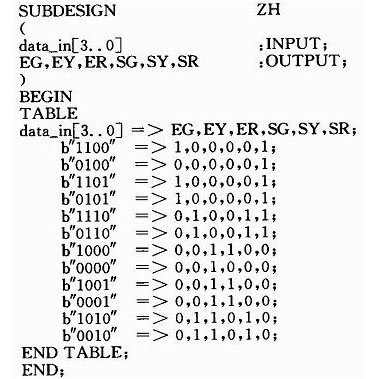

1��3��4 ���ֱȽ�һ���������

��ģ�齫״̬��ʱģ�������ʱ����ʱ��ڵ���бȽϣ��Ӷ�ȷ����·����22 s����16 s�ľ����ij��״̬���ɱ�1��֪������(I)���ϱ�(J)�Ŀ���״̬����3���εĿ��������ֱ��Ӧ3��ʱ��Σ�1��3 s��4��6 s�ʹ���6 s����ˣ��������ֱȽ������бȽϣ�ȷ����ʱֵС��4 s�����6 s��������ͼ7��ʾ������4Ƭ7485���ֱȽ�������������������һ����״̬��ʱģ��������4��������0100�Ƚϣ���һ����״̬��ʱģ��������6��������0110�Ƚϡ�

��д�������ֵ������״̬�ź�S���������ֱȽ��������Y1��Y2��1 Hz������Ϊ���룬�����Ƶ�״̬��Ϊ������Ӷ���������ϵ�ó���Ӧʱ���·��״̬�����ƺ졢�ơ��̵ƴ��ڲ�ͬ��״̬��S�жϵ�·����22 s״̬����16 s״̬��Y1��Y2���ֶ������ϱ�������״̬��1 Hz����ʵ���̵���˸��

2 ��·���鹹�����

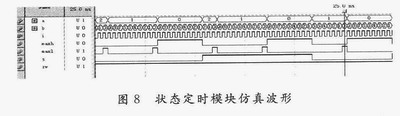

����Quartus��������Ƹ���ģ�飬�����з��档ȷ�Ͻ����������FPGAʵ����У�������Ӧ��Ӳ�����ԣ����Խ�����������һ�¡�ͼ8Ϊ���沨�Σ�ϵͳ�ϵ���Ҫ�����Ĺ��̣���˵�·��������ǰ�ظ���22s��״̬��

����Ķ�:

- ...2012/03/31 10:53������FPGA����Ƶ���������

- ...2011/12/02 16:57������FPGAֱ��������Ƶϵͳ�����

- ...2011/11/07 15:11������FPGA�ĸ��ٴ��д���ϵͳ�������ʵ��

- ...2011/11/07 15:10������FPGA��ͨ���첽�շ������

- ...2011/11/07 15:10������FPGA��Զ�������������ϵͳ���

- ...2011/10/31 16:02������FPGA�����ݲɼ�ϵͳ���

- ...��ͼ����������DZ��屳��ij��漶��ȫ���Ҫ��

- ...��ʹ���а�ȫ���ϵ�����洢������ȫ������ϵͳ

- ...������ƫ�ò�����Դ������Ľ��½�չ��Ӧ��

- ...�����¿�˹����ijƷ�����ܲ���������������ƪ

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��(��)

- ...�����ߵ���ʽ�¶ȼ��������ϵͳ�����ŵ���ʧ���Ӱ��

- ...��RTD����ϵͳ�����ŵ���ʧ���Ӱ��

- ...������BR/EDR �� Bluetooth Smart��ʮ����Ҫ����

- ...�� ��о���������Уδ�������˻�������ƴ���������ʽ����

- ...�� ̽�صڶ�������ɽӥ�����¡����������鼼����̳��

- ...�� ��2018�й��뵼����̬����ᡱ�ڽ���ʡ��������

- ...�� �������¹滮��CITE 2019�t���ǻ�δ��

- ...�� ��������������TI���ײ������������ڴ�������ܵ�����

- ...�� �ⷨ�뵼�壨ST����Cinemo��Valens��CES 2018չ��������ʾ������Ϣ���ֽ������

- ...�� �������ɵ�·��ҵ���·�չ�߷���̳�����ھ��ٿ�

- ...�� ������ǿ�Ƴ���PCIM����2017չ

- ...�� GPGPU����������й�оƬ��ҵ�Ŀհش�

- ...�� ��������Ʒ�����Wi-Fi���ӵ��ĸ��ؼ�����

- ...�� �������й�MEMS���ܴ�������ҵ��չ��ἴ���ڰ��������Ļ

- ...�� IAICר��������й�о��Ӧ�ô��£���Ϣ��ȫ�߷���̳��������

- ...�� ���ܿ�����Դǯλ����

- ...�� ���5G���ײ�OTA ���Լ���

- ...�� ����г����������ƶ�Molex��ǿ��������ķ�չ

- ...�� �й���ɫ�������˳�������ٿ��ڼ� ����ѧ���ù�̽��ɫ��չ��ģʽ

- ...�� Efinix® ȫ������AI��Ե���㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬʱ����Ʒ��չ����ʮ������Ԫ��T200 FPGA

- ...�� Ӣ������������ᣬ�����ǻ�������

- ...�� �����Ʒ�������������ֻᱱ������Դר���ɹ�����

- ...�� Manz���ǿƼ�����뵼������ Ϊ��弶�ȳ��ͷ�װ�ṩ��ѧʪ�Ƴ̡�Ϳ��������Ӧ�õ������豸�������

- ...�� �е���BITRODE������ز���ϵͳ˳��������������Դ

- ...�� �е���FTFϵ�е�ز���ϵͳ�б걱������Դ�����ɷ�����˾

- ...�� �е����ʸ�ѹ��Դ����ʽ����ϵͳ�ɹ������е���è

- ...�� �е������ڵ綯�������ؼ������������ֻ��������Ƚ���������